4軸 / 2軸 モーションコントロールLSI

# X7043A / X7023A

ユーザーズマニュアル Rev.1.0

MNLX7000A131001

# 目 次

| <u>1.</u>  | X704 | 3A/X7023A の概要                 | 2  |

|------------|------|-------------------------------|----|

|            | 1-1  | はじめに                          | 2  |

|            | 1-2  | 特長                            | 2  |

|            | 1-3  | ブロック図                         | 4  |

|            |      | 1-3-1 全体ブロック図と入出力信号           | 4  |

|            |      | 1−3−2 # 1 ~ 4 軸回路ブロック図        | 4  |

|            | 1-4  | 仕様一覧                          | 5  |

|            | 1-5  | パッケージ外形図                      | 6  |

|            |      | 1-5-1 X7043A                  | 6  |

|            |      | 1-5-2 X7023A                  | 7  |

|            | 1-6  | ピン配置および端子説明                   | 8  |

|            |      | 1-6-1 端子説明                    | 8  |

|            |      | 1-6-2 ピン配置                    | 12 |

|            | 1-7  | システムの構成                       | 13 |

|            | 1-8  | CPU とのインターフェース例               | 14 |

|            |      | 1-8-1 Z80 とのインターフェース例         | 14 |

|            |      | 1-8-2 68000 とのインターフェース例       | 14 |

| <u>2.</u>  | アド   | レス割付とデータのリード・ライト              | 15 |

|            | 2-1  | アドレス割付表                       | 15 |

| <u>3.</u>  | コマ   | ンドの種類と機能                      | 16 |

|            | 3-1  | コマンドのライト                      | 16 |

|            | 3-2  | コマンドー覧                        | 16 |

| <b>4</b> . | 各種   | レジシタと内部カウンタについて               | 22 |

|            | 4-1  | レジスタとカウンタの一覧                  | 22 |

|            | 4-2  | レジスタとカウンタのリード・ライト             | 23 |

|            |      | 4-2-1 1バイトのレジスタのリードとライト       |    |

|            |      | 4-2-2 2 バイトのレジスタのリードとライト      |    |

|            |      | 4-2-3 3 バイトのレジスタとカウンタのリードとライト | 23 |

|            |      | 4-2-4 4 バイトのカウンタのリードとライト      | 23 |

|            |      |                               |    |

| <u>5.</u> | パル   | ス出る           | カに関する各パラメータについて         | 24 |

|-----------|------|---------------|-------------------------|----|

|           | 5-1  | パラ            | メータの種類                  | 24 |

|           |      | 5-1-1         | 周波数倍率設定レジスタ(R0 レジスタ)    | 24 |

|           |      | 5-1-2         | 出力パルス数設定レジスタ(R1 レジスタ)   | 24 |

|           |      | 5-1-3         | 減速開始点設定レジスタ(R2 レジスタ)    | 24 |

|           |      | 5-1-4         | 起動周波数設定レジスタ(R3 レジスタ)    | 24 |

|           |      | 5-1-5         | 最高周波数設定レジスタ(R4 レジスタ)    | 24 |

|           |      | 5-1-6         | 加速レート設定レジスタ(R5 レジスタ)    | 25 |

|           |      | 5-1-7         | 減速レート設定レジスタ(R6 レジスタ)    | 25 |

|           |      | 5-1-8         | S 字加減速区間設定レジスタ(R7 レジスタ) | 25 |

|           |      | 5-1-9         | 直線補間基数設定レジスタ(R8 レジスタ)   | 25 |

|           | 5-2  | パラ            | メータの計算式                 | 26 |

| <u>6.</u> | 初期   | 設定し           | レジスタについて                | 27 |

|           | 6-1  | 各初期           | 期設定レジスタの機能              | 27 |

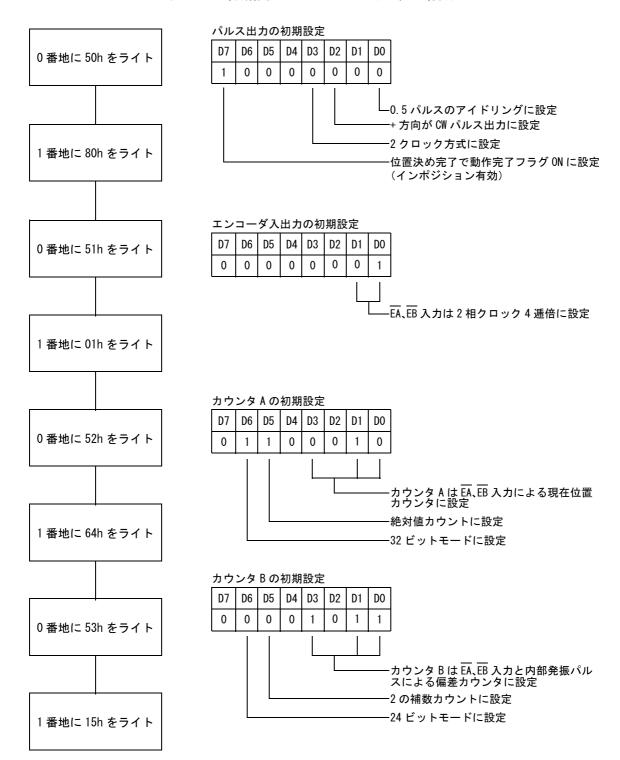

|           |      | 6-1-1         | パルス出力初期設定レジスタ           | 27 |

|           |      | 6-1-2         | エンコーダ入出力の初期設定レジスタ       | 28 |

|           |      | 6-1-3         | カウンタ A、B 初期設定レジスタ       | 28 |

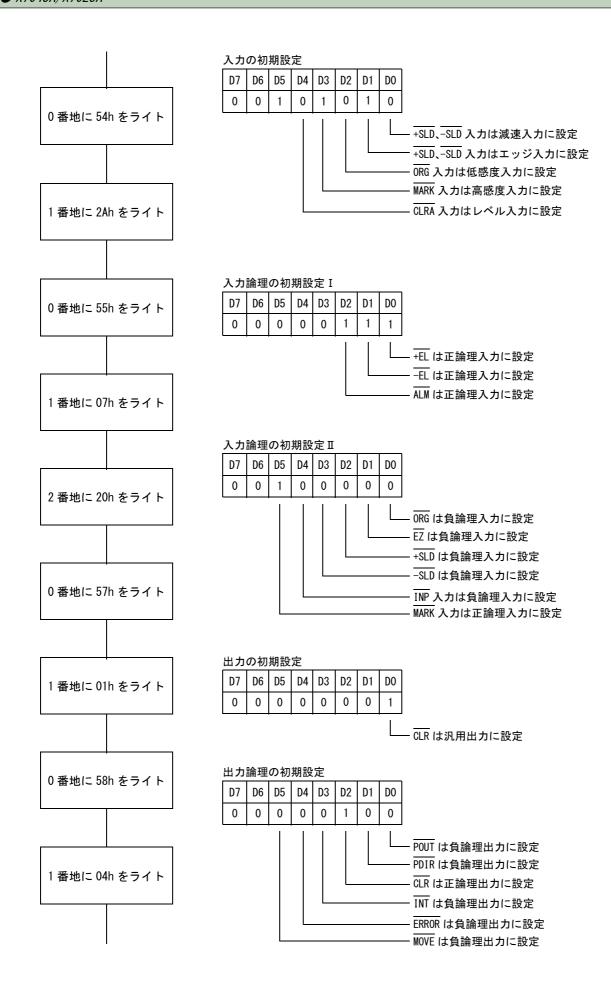

|           |      | 6-1-4         | 入力の初期設定レジスタ             | 29 |

|           |      | 6-1-5         | 入力論理の初期設定レジスタⅠ、Ⅱ        | 30 |

|           |      | 6-1-6         | 入力フィルタの初期設定レジスタ(F)      | 30 |

|           |      | 6-1-7         | 出力の初期設定レジスタ             | 31 |

|           |      | 6-1-8         | 出力論理の初期設定レジスタ           | 31 |

| 7         | 生145 | <b>工</b> [    | ドレジフタについて               | 20 |

| <u>/.</u> | 刊1叫  | <del></del> 1 | ドレジスタについて               | 32 |

|           | 7-1  | 各制征           | 御モードレジスタの機能             | 32 |

|           |      | 7-1-1         | 動作制御モード設定レジスタ           | 32 |

|           |      | 7-1-2         | カウンタ A、B の制御レジスタ        | 34 |

|           |      | 7-1-3         | CLR 出力制御モードレジスタ         | 34 |

|           |      | 7-1-4         | コンパレータ制御モード設定レジスタ       | 35 |

| 8. 害        | 削り込   | 込み機能について                | 36 |

|-------------|-------|-------------------------|----|

|             | 8-1 4 | 各割り込みマスクレジスタ            | 36 |

|             | 8     | 3-1-1 パルス発振割り込みマスクレジスタ  | 36 |

|             | 8     | 3-1-2 カウンタ割り込みマスクレジスタ   | 36 |

|             | 8     | 3-1-3 センサ割り込みマスクレジスタ    | 37 |

|             | 8     | 3-1-4 コンパレータ割り込みマスクレジスタ | 37 |

|             | 8-2 4 | 各割り込みフラグレジスタ            | 38 |

|             | 8     | 3-2-1 パルス発振割り込みフラグレジスタ  | 38 |

|             | 8     | 3-2-2 カウンタ割り込みフラグレジスタ   | 38 |

|             | 8     | 3-2-3 センサ割り込みフラグレジスタ    | 39 |

|             | 8     | 3-2-4 コンパレータ割り込みフラグレジスタ | 39 |

| <u>9. 7</u> | ステー   | -タスレジスタについて             | 40 |

|             | 9-1 3 | 主ステータス                  | 40 |

|             | 9     | 9−1−1 動作状態ステータス         | 40 |

|             | 9     | 9-1-2 割り込み状態ステータス       | 40 |

|             | 9     | 9-1-3 割り込み軸ステータス        | 41 |

|             | 9-2 1 | 補助ステータス                 | 42 |

|             | 9     | 9−2−1 センサ状態ステータス        | 42 |

|             | 9     | 9−2−2 正常停止要因ステータス       | 43 |

|             | 9     | 9-2-3 エラー停止要因ステータス      | 43 |

|             | 9     | 9-2-4 汎用入力状態ステータス       | 44 |

|             | 9     | 9-2-5 コンパレータ状態ステータス     | 44 |

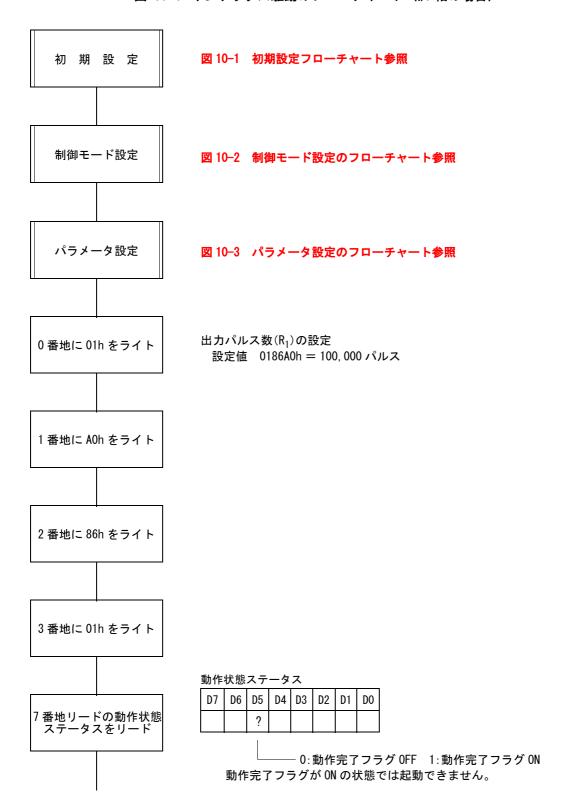

| 10.         | アプ    | リケーション例                 | 45 |

|             | 10-1  | 初期設定                    | 45 |

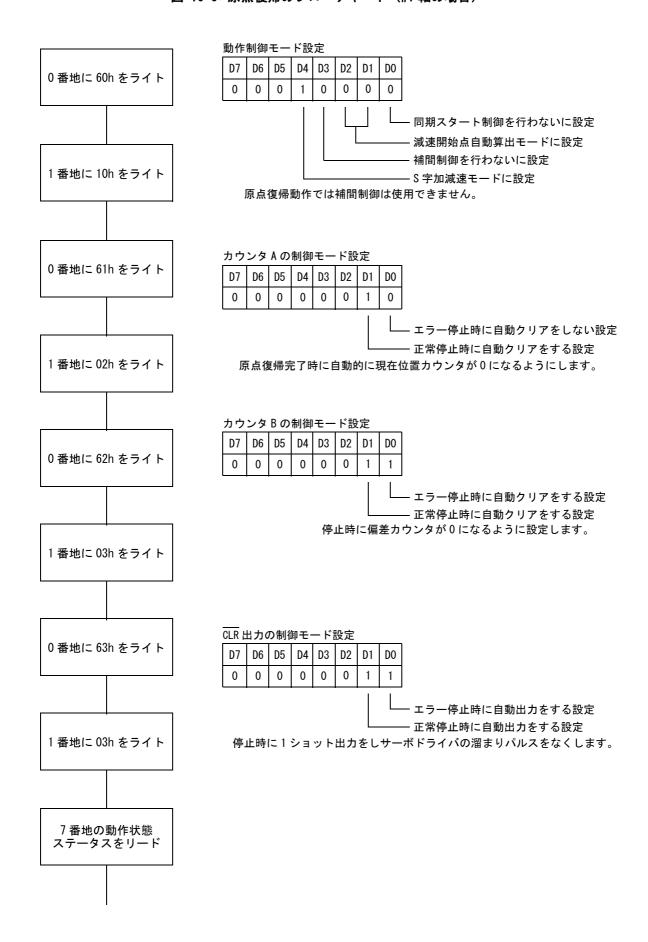

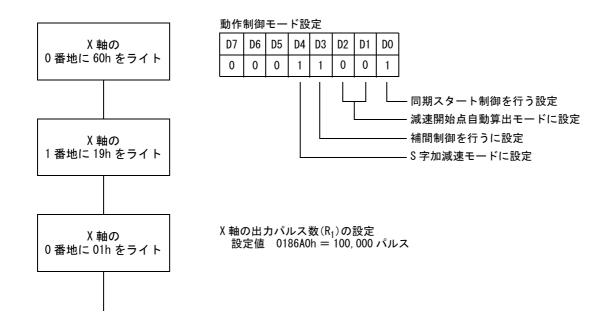

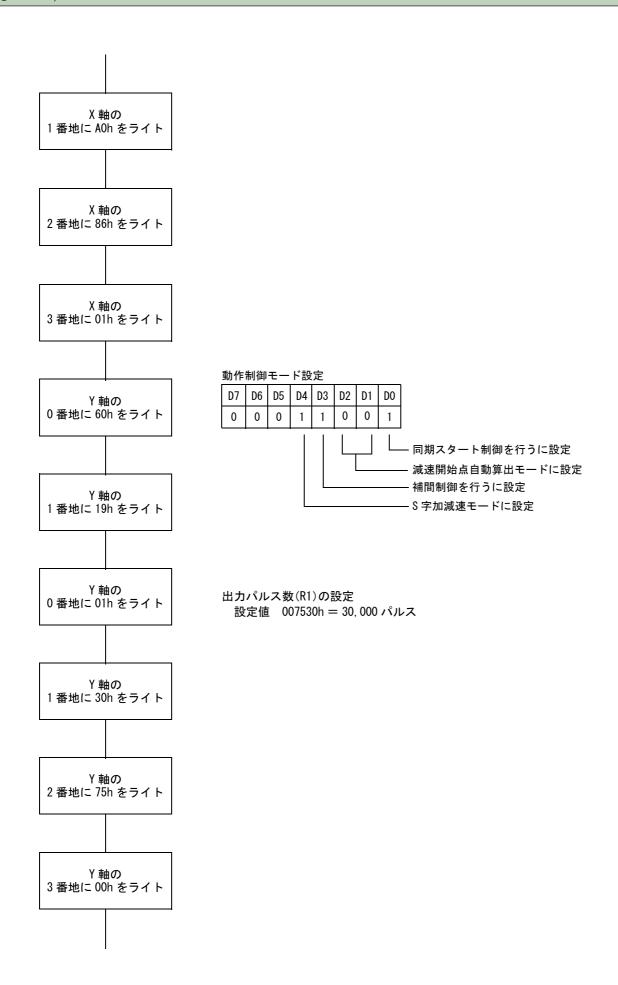

|             | 10-2  | 制御モード設定                 | 47 |

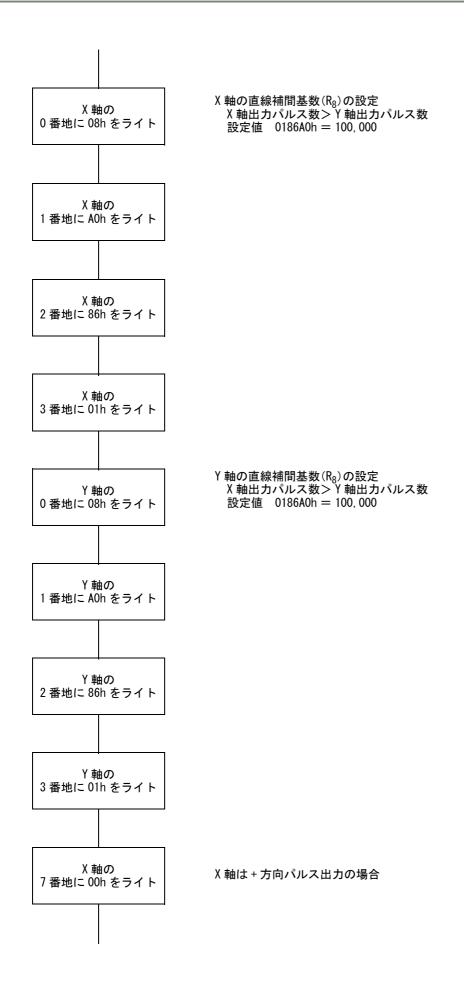

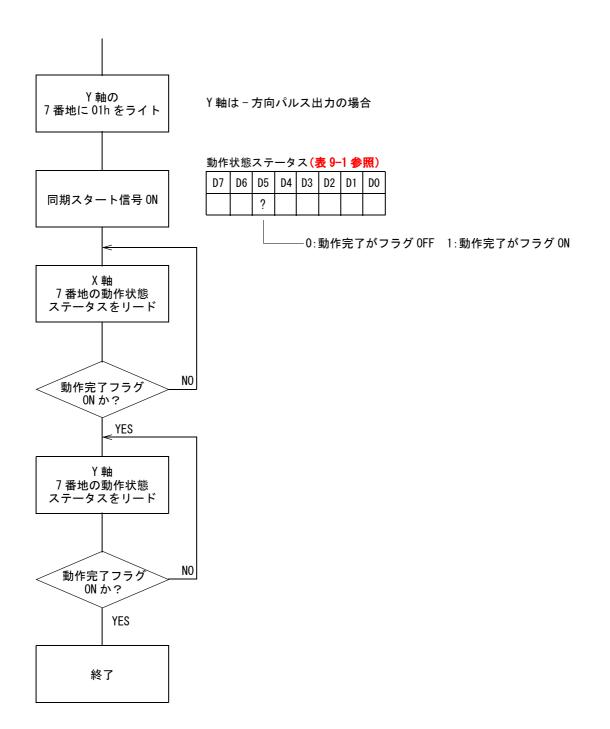

|             | 10-3  | パラメータの設定                | 49 |

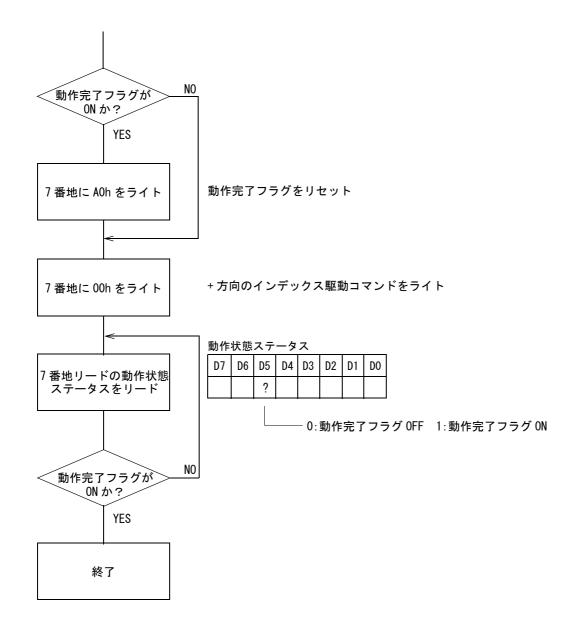

|             | 10-4  | インデックス駆動                | 52 |

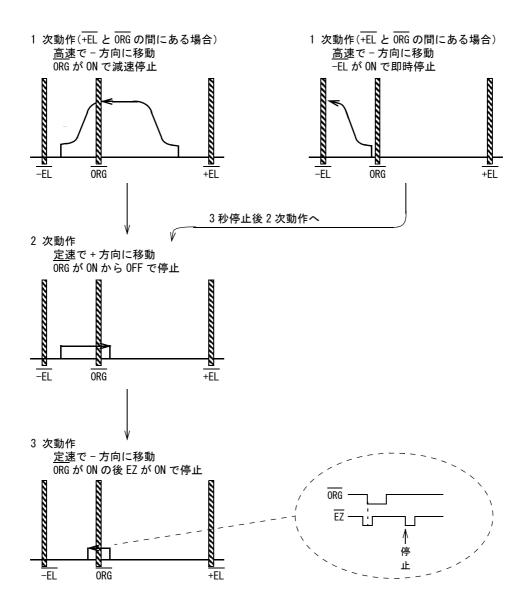

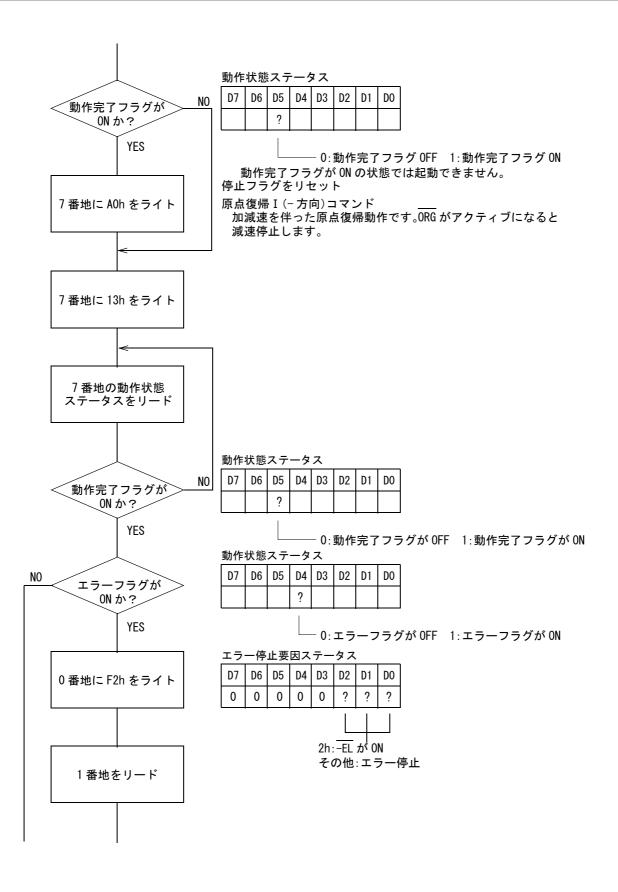

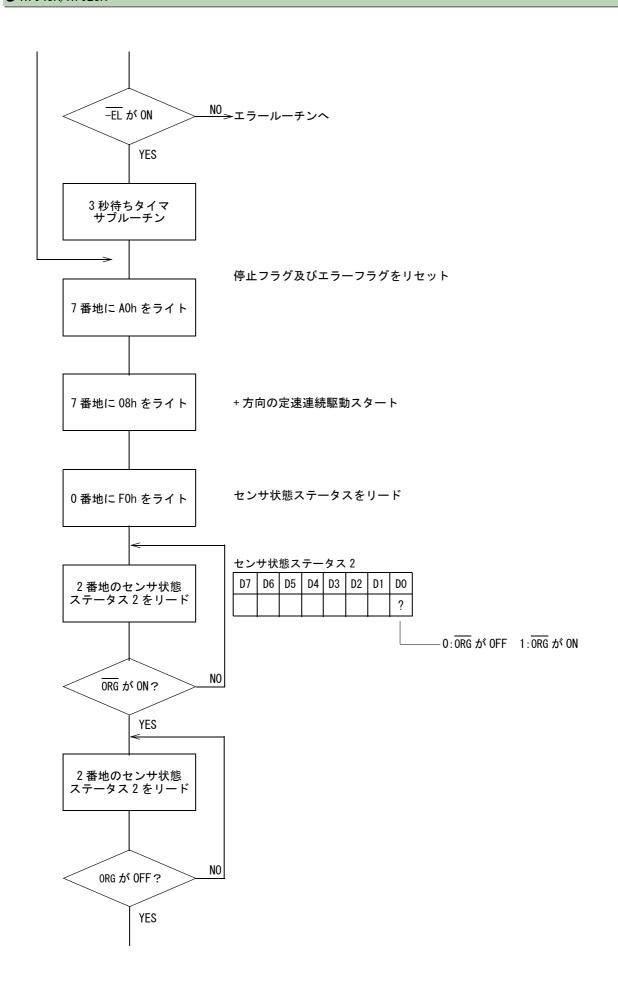

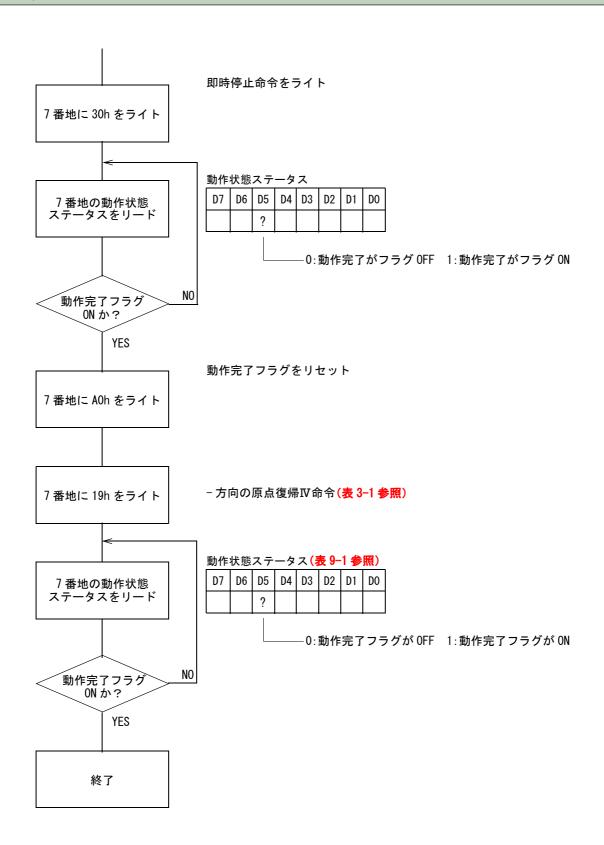

|             | 10-5  | 原点復帰動作                  | 54 |

|             | 10-6  | 直線補間駆動                  | 59 |

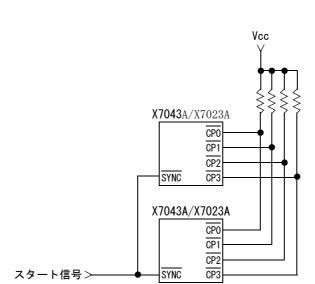

|             | 1     | 10-6-1 ハードウェアの注意点       | 59 |

|             | 1     | 10−6−2 直線補間駆動のフロー       | 60 |

| <u>11.</u> | 電気的特性                                          | 64 |

|------------|------------------------------------------------|----|

|            | 11−1 絶対最大定格(Vss=0V)                            | 64 |

|            | 11-2 推奨動作条件(Vss=0V)                            | 64 |

|            | 11−3 DC 特性                                     | 65 |

|            | 11-3-1 DC 特性(VddIO=5V ± 10%、Ta=-40 ~ +85 ℃)    | 65 |

|            | 11-3-2 DC 特性(VddIO=3.3V ± 10%、Ta=-40 ~ +85 °C) | 66 |

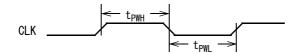

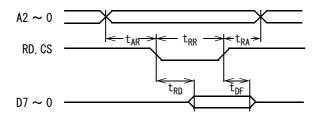

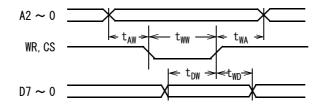

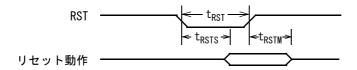

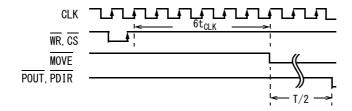

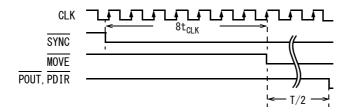

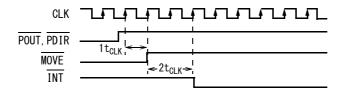

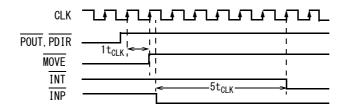

|            | 11−4 スイッチング特性                                  | 67 |

|            | 11-4-1 CPU インターフェース                            | 67 |

|            | 11-4-2 CPU インターフェース                            |    |

|            | 11-4-3 エンコーダインターフェース                           | 68 |

|            | 11-4-4 入出カインターフェース                             | 70 |

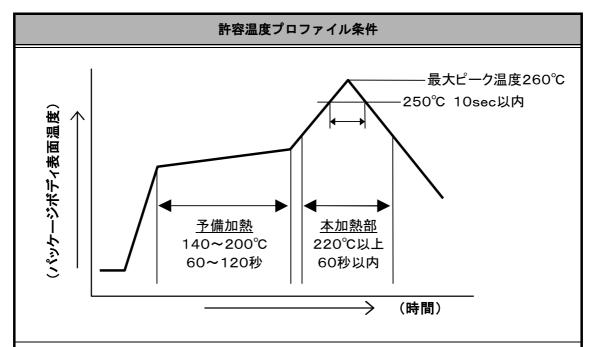

| <u>12.</u> | 本製品のはんだ付け実装における注意事項                            | 71 |

| 13.        | 改訂履歴                                           | 72 |

#### - 本製品の主な環境影響化学物質の不使用状況 -

- 1. 欧州 RoHs 指令 (2011/65/EU) に対応しています。

- 2. 欧州包装材指令(94/62/EC)、米国包装材規制に対応しています。

- 3. 本製品の製造工程において、以下のオゾン層破壊物質は使用しておりません。

- ・モントリオール議定書 附属書 A, B, E, C- Ⅱ, C- Ⅲに記載されている物質

- ・代替フロン(モントリオール議定書 附属書 C- I)

- 4. 本製品には、以下の化学物質を使用しておりません。

- ・アスベスト

- 紫外線吸収剤 2-(2H-1,2,3- ベンゾトリアゾール -2- イル )-4,6- ジ -tert- ブチルフェノール

- ・テトラクロロ無水フタル酸、ヘキサクロロベンゼン (HCB)(118-74-1)

- 5. 本製品には、PFOS の含有および残留はありません。

# 1. X7043A/X7023A の概要

#### 1-1 はじめに

X7043A/X7023A は、パルス列入力型サーボモータ及びステッピングモータの速度制御と位置決め制御を目的とするパルス発生 LSI です。X7043A は 4 軸、X7023A は 2 軸の制御が可能です。

内部構成は、S字または直線加減速パルス発生器、直線補間分周器、台形または三角駆動の自動減速点算出器、現在位置カウンタや偏差カウンタとして使用できる2本のマルチカウンタとエンコーダ入力コンバータ、原点復帰センサインターフェース、リミットセンサインターフェース、サーボドライバインターフェース、8ビット汎用入力と8ビット汎用出力を備えています。

ホスト CPU とのインターフェースが用意されていますので周辺 LSI として使用できます。

#### 1-2 特長

◇ CPU インターフェース

●対象マイコン 80 系、68 系など

●アドレス占有域 X7043A は 5 ビット(32 バイト)、

X7023A は 4 ビット(16 バイト)

●データビット幅 8ビット

#### ◇駆動命令

- ●インデックス駆動

- ●連続パルス駆動

- ●原点復帰駆動

- ●センサ位置決め駆動

#### ◇駆動モード

●加減速モード S字(正弦、放物線)、直線

●減速開始点 自動算出、マニュアル設定、オフセット設定

●同期モード 多軸直線補間、同期スタート

#### ◇エンコーダカウンタ

●カウンタ数 各軸に2本

●ビット長 24 ビット、32 ビット切り替え式

●カウント入力 内部パルス単独、外部入力パルス単独、内部パルスと外部入力パルス

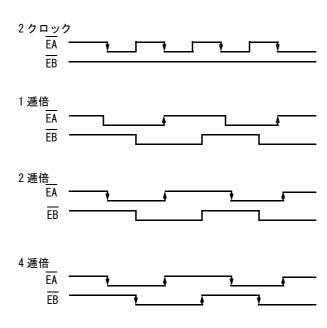

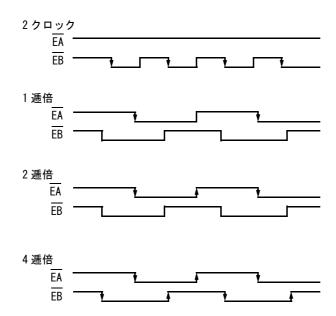

#### ◇エンコーダコンバータ入力

●チャンネル数 1 チャンネル

●入力形態 2 クロック、90° 位相差 2 相クロック

●逓倍 1 逓倍、2 逓倍、4 逓倍

◇コンパレータ

●ビット長 24 ビット

●比較対象 レジスタとカウンタ、カウンタとカウンタ

●比較方式 =,>

●比較出力 1点(=または>)

♦ I/O

●入力 8点 8点 ●出力

#### ◇その他

●加速、減速別設定機能

●タイマ機能

●入力フィルタ機能

●割り込み機能

●入出力論理切り替え

●各種ステータス機能

◇クロック 20.0MHz(MAX)、推奨 16.384MHz または 19.6608MHz

◇テクノロジー CMOS

◇電源 内部電圧:3.3V ± 10% IO 電圧:5V ± 10% または 3.3V ± 10%

-40 **~** +85 °C ◇動作温度範囲

◇パッケージ X7043A 144pin LQFP 20 × 20 × 1.7、 0.5 ピッチ(mm)

X7023A 100pin TQFP 14 × 14 × 1.2、 0.5 ピッチ(mm)

鉛フリー& ハロゲンフリー仕様

# 1-3 ブロック図

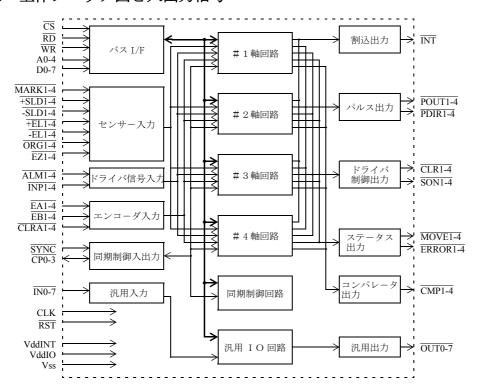

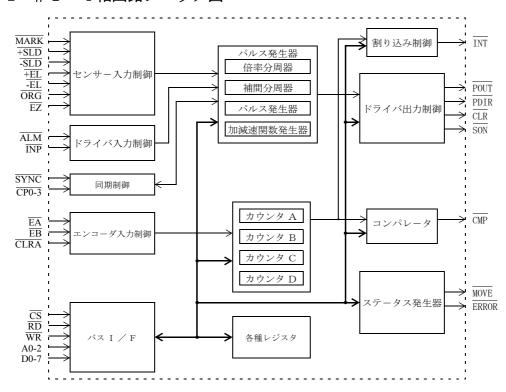

図 1-1: ブロック図

#### 1-3-1 全体ブロック図と入出力信号

#### 1-3-2 #1~4軸回路ブロック図

X7043A は #1 ~ 4 軸、X7023A は #1 ~ 2 軸となります。

# 1-4 仕様一覧

表 1-1: 仕様一覧

| 項目                                          | 内容                                                       |  |  |  |  |

|---------------------------------------------|----------------------------------------------------------|--|--|--|--|

| 電源電圧                                        | 内部電圧 3.3V ± 10% IO 電圧 5V ± 10% または 3.3V ± 10%            |  |  |  |  |

| 入力レベル                                       | TTL レベル(5VIO)、LVTTL(3.3VIO)                              |  |  |  |  |

| 出力レベル                                       | CMOS レベル(5VIO)、LVCMOS レベル(3.3VIO)                        |  |  |  |  |

| 最大入力クロック(f)                                 | 20.0MHz(MAX)、推奨 16.384MHz または 19.6608MHz                 |  |  |  |  |

| ┃<br>┃最大出力周波数                               | 直線加減速 5Mpps                                              |  |  |  |  |

| 取入山刀局 <i>放</i> 致<br>                        | S 字加減速 3.05Mpps                                          |  |  |  |  |

| 加減速時間                                       | 約 8msec ~ 131sec                                         |  |  |  |  |

| 加級逐時间                                       | (但し、16382 ステップ。 f = 16.384MHz)                           |  |  |  |  |

| 出力パルス数設定範囲(R <sub>1</sub> )                 | 1 ~ 16,777,215                                           |  |  |  |  |

| 減速開始点設定範囲(R <sub>2</sub> )                  | 0~16,777,215 (マニュアル設定)                                   |  |  |  |  |

| / 《                                         | -8388608 ~ 8388607 (自動算出オフセット設定)                         |  |  |  |  |

| 周波数倍率設定範囲 $(R_0)$                           | 1 ~ 4095                                                 |  |  |  |  |

| 周波数設定ステップ数(R <sub>3</sub> ,R <sub>4</sub> ) | 直線加減速·S 字加減速かつ減速点マニュアル設定 1 ~ 16383                       |  |  |  |  |

| 河収奴改たヘブツン奴(R <sub>3</sub> ,R <sub>4</sub> ) | S 字加減速かつ減速開始点自動算出モード 1 ~ 10000                           |  |  |  |  |

| 加減速レート設定範囲(R <sub>5</sub> ,R <sub>6</sub> ) | 1 ~ 16383                                                |  |  |  |  |

| S 字区間設定範囲(R <sub>7</sub> )                  | 1 ~ 8191                                                 |  |  |  |  |

|                                             | 0 ~ 255                                                  |  |  |  |  |

| センサ入力感度設定範囲(F)                              | 約 $0.98 \sim 250 \mu \text{sec} (f = 16.384 \text{MHz})$ |  |  |  |  |

|                                             | 出力 クロック出力 ゲートコントロール/2クロック切替え可。                           |  |  |  |  |

|                                             | <br>  論理切替え可。                                            |  |  |  |  |

|                                             | 1 ショット出力 約 1.9 µ sec (f = 16.384MHz)                     |  |  |  |  |

| ドライバインターフェース                                | 論理切替え可。                                                  |  |  |  |  |

|                                             |                                                          |  |  |  |  |

|                                             | サーボ ON 出力 汎用出力。                                          |  |  |  |  |

|                                             | 入力 ドライバアラーム入力 各軸に1点。 論理切替え可。                             |  |  |  |  |

|                                             | 位置決め完了入力 各軸に1点。 論理切替え可。                                  |  |  |  |  |

|                                             | エンドリミット入力 各軸に 2 点。+方向、-方向。 論理切替え可。                       |  |  |  |  |

|                                             | スローダウン入力 各軸に2点。+方向、一方向。論理切替え可。                           |  |  |  |  |

| センサ入力                                       | スローダウン、スローダウン停止切替え可。                                     |  |  |  |  |

|                                             | <br>  原点入力   各軸に2点。オリジン、Z相。論理切替え可。                       |  |  |  |  |

|                                             | <br>  マークセンサ入力 各軸に1点。論理切替え可。                             |  |  |  |  |

|                                             | 入力 8点                                                    |  |  |  |  |

| 汎用入出力                                       | 出力 8点                                                    |  |  |  |  |

| エンコーダインターフェース                               | 入力   各軸に 1 チャンネル。2 クロック、1、2、4 逓倍                         |  |  |  |  |

|                                             | 同期スタート入力 1点                                              |  |  |  |  |

| その他の入出力                                     | <br>  カウンタクリア入力 各軸に1点                                    |  |  |  |  |

|                                             | コンパレータ出力 各軸に1点                                           |  |  |  |  |

| <br>】動作温度                                   | -40 ~ +85 °C                                             |  |  |  |  |

| 保存温度                                        | -65 ~ +150 °C                                            |  |  |  |  |

|                                             | X7043A 144PIN LQFP 20 × 20(mm)                           |  |  |  |  |

| 】<br>形  状                                   | X7023A 100PIN TQFP 14 × 14(mm)                           |  |  |  |  |

|                                             | 鉛フリー&ハロゲンフリー仕様                                           |  |  |  |  |

|                                             | 如フラーなハロフンフラーは1水                                          |  |  |  |  |

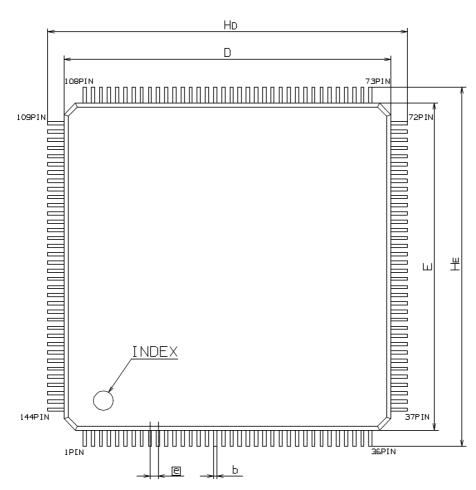

# 1-5 パッケージ外形図

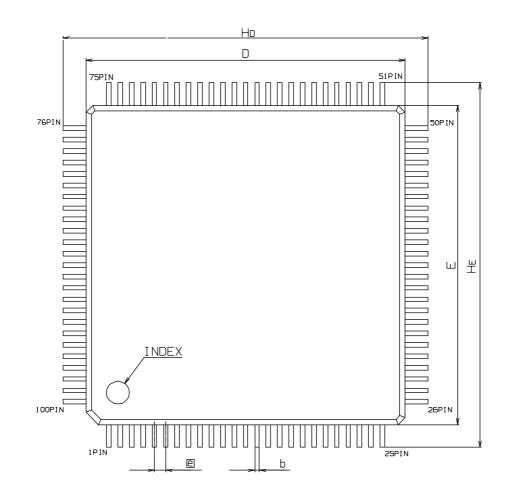

#### 1-5-1 X7043A

図 1-2: パッケージ外形図 (P-LQFP144-2020-0.50)

( 単位 mm )

|                | Dimens | ion in Mil | limeters      |

|----------------|--------|------------|---------------|

| Symbol         | Min    | Nom        | Ma×           |

| E              | -      | 20         | -             |

| D              | -      | 20         | -             |

| Amax           | -      | ı          | 1.7           |

| A <sub>1</sub> | -      | 0.1        | -             |

| A2             | -      | 1.4        | -             |

| e              | -      | 0.5        | -             |

| Ь              | 0.17   | -          | 0.27          |

| C              | 0.09   | -          | 0.2           |

| Φ              | 0°     | 1          | 10°           |

| L              | 0.3    | -          | 0. <i>7</i> 5 |

| L <sub>1</sub> | _      | 1          | -             |

| HE             | _      | 22         | -             |

| Ho             | -      | 22         | -             |

| У              | -      | 1          | 0.08          |

$1 = 1 \, \text{mm}$

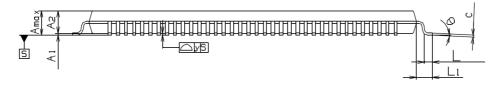

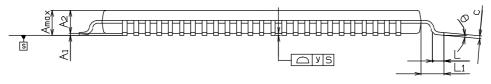

#### 1-5-2 X7023A

図 1-3: パッケージ外形図 (P-TQFP100-1414-0.50)

( 単位 mm )

| C              | Dimension in Millimeter |     |      |  |  |  |  |

|----------------|-------------------------|-----|------|--|--|--|--|

| Symbol         | Min                     | Nom | Max  |  |  |  |  |

| E              | -                       | 14  | -    |  |  |  |  |

| D              | -                       | 14  | -    |  |  |  |  |

| Amax           | -                       | -   | 1.2  |  |  |  |  |

| A <sub>1</sub> | -                       | 0.1 | -    |  |  |  |  |

| A <sub>2</sub> | -                       | 1   | -    |  |  |  |  |

| e              | -                       | 0.5 | -    |  |  |  |  |

| Ь              | 0.13                    | -   | 0.27 |  |  |  |  |

| С              | 0.09                    | -   | 0.2  |  |  |  |  |

| θ              | 0,                      | -   | 10°  |  |  |  |  |

| L              | 0.3                     | -   | 0.75 |  |  |  |  |

| Lı             | -                       | 1   | -    |  |  |  |  |

| HE             | -                       | 16  | -    |  |  |  |  |

| Ho             | -                       | 16  | -    |  |  |  |  |

| У              | -                       | -   | 0.08 |  |  |  |  |

# 1-6 ピン配置および端子説明

### 1-6-1 端子説明

表 1-2: 端子説明

| ———————————————————————————————————— |                |                        |     |                                |                                          |   |   |   |   |   |     |                                   |

|--------------------------------------|----------------|------------------------|-----|--------------------------------|------------------------------------------|---|---|---|---|---|-----|-----------------------------------|

| 端子番号<br>                             |                | 信号名 I/O                |     | 論理                             | 内 容                                      |   |   |   |   |   |     |                                   |

| X7043A                               | X7023A         | T. I. ID. IT.          |     |                                |                                          |   |   |   |   |   |     |                                   |

| 54,126                               | 37,87          | VddINT                 | _   |                                | +3.3V ± 5% 電源入力です。                       |   |   |   |   |   |     |                                   |

| 7,19,46,                             | 7,18,          | VI-LIO                 |     |                                | . cv. l co/ ++ l+ 2 237 l co/ 南海 1 + 本+  |   |   |   |   |   |     |                                   |

| 58,79,98,                            | 44,54,         | VddIO                  | _   | +5V ± 5% または 3.3V ± 5% 電源入力です。 |                                          |   |   |   |   |   |     |                                   |

| 117,138<br>9,14,21,                  | 73,94<br>9,20, |                        |     |                                |                                          |   |   |   |   |   |     |                                   |

|                                      |                |                        |     |                                |                                          |   |   |   |   |   |     |                                   |

| 30,47,55,<br>59,80,99,               | 28,38,         | Man                    |     |                                | OV. EVE. 1 L. T. L.                      |   |   |   |   |   |     |                                   |

|                                      | 45,55,         | Vss                    | _   |                                | 0V 電源入力です。                               |   |   |   |   |   |     |                                   |

| 118,127,                             | 74,88,         |                        |     |                                |                                          |   |   |   |   |   |     |                                   |

| 139                                  | 95             |                        |     |                                | 甘進り中にたる土で土 日上る 上田冲粉 200 ほ                |   |   |   |   |   |     |                                   |

| 8                                    | 8              | CLK                    | I   | 正                              | 基準クロック入力です。最大入力周波数 20MHz。                |   |   |   |   |   |     |                                   |

|                                      |                |                        |     |                                | デューティ50 ± 10%                            |   |   |   |   |   |     |                                   |

| 20                                   | 19             | RST                    | I   | 負                              | リセット信号です。基準クロックの 3 周期以上の Low 入力          |   |   |   |   |   |     |                                   |

|                                      |                |                        |     |                                | により本 LSI は初期化されます。                       |   |   |   |   |   |     |                                   |

| 27                                   | 25             | CS                     | I   | 負                              | チップセレクト信号です。この端子が Low になる事により            |   |   |   |   |   |     |                                   |

|                                      |                |                        |     |                                | 本 LSI にアクセスできます。                         |   |   |   |   |   |     |                                   |

| 28                                   | 26             | $\overline{\text{RD}}$ | I   | 負                              | リードイネーブル信号です。CS が Low でかつ RD が Low       |   |   |   |   |   |     |                                   |

|                                      |                |                        |     |                                | の時にデータの読み出しができます。                        |   |   |   |   |   |     |                                   |

| 29                                   | 27             | WR                     | I   | 負                              | ライトイネーブル信号です。CS が Low の時、WR が            |   |   |   |   |   |     |                                   |

| 26                                   | 2.1            |                        |     |                                | Low から High になるエッジでデータを取り込みます。           |   |   |   |   |   |     |                                   |

| 26                                   | 24             | A0                     |     |                                |                                          |   |   |   |   |   |     |                                   |

| 25                                   | 23             | A1                     |     |                                |                                          |   |   |   |   |   |     |                                   |

| 24                                   | 22             | A2                     | I E | I                              | I                                        | 1 | 正 | 正 | 正 | 正 | I Œ | A0(LSB)から A4(MSB)の 5 ビットアドレスバスです。 |

| 23                                   | 21             | A3                     |     |                                |                                          |   |   |   |   |   |     |                                   |

| 22                                   | -              | A4                     |     |                                |                                          |   |   |   |   |   |     |                                   |

| 18                                   | 17             | D0                     |     |                                |                                          |   |   |   |   |   |     |                                   |

| 17                                   | 16             | D1                     |     |                                |                                          |   |   |   |   |   |     |                                   |

| 16                                   | 15             | D2                     |     |                                | <br>  ホスト CPU との間でデータ転送を行う DO(LSB) から D7 |   |   |   |   |   |     |                                   |

| 15                                   | 14             | D3                     | I/O | Œ                              | (MSB)の8ビット双方向性データバスです。この端子の出             |   |   |   |   |   |     |                                   |

| 13                                   | 13             | D4                     |     |                                | カバッファはトライステートになっています。                    |   |   |   |   |   |     |                                   |

| 12                                   | 12             | D5                     |     |                                | 73 7 / 161 / 171 / 111C/6 / CV-6 7 0     |   |   |   |   |   |     |                                   |

| 11                                   | 11             | D6                     |     |                                |                                          |   |   |   |   |   |     |                                   |

| 10                                   | 10             | D7                     |     |                                |                                          |   |   |   |   |   |     |                                   |

|                                      |                |                        |     |                                | 割り込み要求信号です。パルス出力、カウンタ、センサ、コン             |   |   |   |   |   |     |                                   |

|                                      |                |                        |     | パレータの各要因によりアクティブになります。こ        |                                          |   |   |   |   |   |     |                                   |

|                                      |                |                        |     |                                | は Low またはハイインピーダンスの状態になります。              |   |   |   |   |   |     |                                   |

| 31                                   | 29             | INT                    | О   | 正負                             | この INT 出力は割り込み制御レジスタによりマスクするこ            |   |   |   |   |   |     |                                   |

|                                      |                |                        |     |                                | とが出来ます。また、割り込み要因ごとの割り込みフラグリ              |   |   |   |   |   |     |                                   |

|                                      |                |                        |     |                                | セットコマンドを書き込むことにより割り込み要求を解除               |   |   |   |   |   |     |                                   |

|                                      |                |                        |     |                                | できます。                                    |   |   |   |   |   |     |                                   |

表 1-2: 端子説明

| 端子番号       |        |                                     |     |            |                                                            |

|------------|--------|-------------------------------------|-----|------------|------------------------------------------------------------|

| X7043A     | X7023A | 信号名                                 | I/O | 論理         | 内 容                                                        |

| 143        | 99     | ALM1                                |     |            | <u></u><br>ドライバアラーム用の非常停止入力です。入力の論理は入                      |

| 122        | 78     | ALM2                                | _   |            | 力論理設定レジスタで切り替えができます。入力の感度は、                                |

| 103        | -      | ALM3                                | I   | 正負         | 入力感度設定レジスタにより基準クロック周期の 16~                                 |

| 84         | -      | ALM4                                |     |            | 4096 倍まで設定ができます。                                           |

| 136        | 92     | +EL1                                |     |            | + 方向の即時停止エンドリミット入力です。入力の論理は                                |

| 115        | 71     | +EL2                                | ,   | T #        | 入力論理設定レジスタで切り替えができます。入力の感度                                 |

| 96         | -      | +EL3                                | I   | 正負         | は、入力感度設定レジスタにより基準クロック周期の 16~                               |

| 77         | -      | +EL4                                |     |            | 4096 倍まで設定ができます。                                           |

| 135        | 91     | -EL1                                |     |            | - 方向の即時停止エンドリミット入力です。入力の論理は入                               |

| 114        | 70     | -EL2                                | I   | 工名         | 力論理設定レジスタで切り替えができます。入力の感度は                                 |

| 95         | -      | -EL3                                | 1   | 正負         | 入力感度設定レジスタにより基準クロック周期の 16~                                 |

| 76         | -      | -EL4                                |     |            | 4096 倍まで設定ができます。                                           |

| 134        | 90     | +SLD1                               |     |            | + 方向のスローダウンリミット入力です。スローダウンま                                |

| 113        | 69     | +SLD2                               |     |            | たはスローダウン停止の切り替えは入力モード設定レジス                                 |

| 94         | _      | +SLD3                               | I   | 正負         | タでできます。入力の感度は、入力感度設定レジスタにより                                |

| 75         | _      | +SLD4                               |     |            | 基準クロック周期の 16 ~ 4096 倍まで設定ができます。レ                           |

|            |        |                                     |     |            | ベルまたはエッジ動作です。                                              |

| 133        | 89     | -SLD1                               |     |            | - 方向のスローダウンリミット入力です。スローダウンまた                               |

| 112        | 68     | -SLD2                               |     |            | はスローダウン停止の切り替えは入力モード設定レジスタ                                 |

| 93         | -      | -SLD3                               | I   | 正負         | でできます。入力の感度は、入力感度設定レジスタにより基                                |

| 74         | -      | -SLD4                               |     |            | 準クロック周期の 16 ~ 4096 倍まで設定ができます。レベ                           |

| 127        | 02     |                                     |     |            | ルまたはエッジ動作です。                                               |

| 137<br>116 | 93     | ORG1                                |     |            | 原点センサ入力です。機械原点復帰駆動では、ORG 入力単                               |

|            | 72     | ORG2<br>ORG3                        | I   | 正負         | 独の原点復帰動作と ORG 入力と EZ(エンコーダ Z 相)入力                          |

| 97         | -      | ORG4                                |     |            | とで行う原点復帰動作が有ります。エッジ動作です。                                   |

| 78         | -      | ORGI                                |     |            | 入力の感度は基準クロックの 1 または 16 周期です。                               |

| 140        | 96     | EZ1                                 |     |            | エンコーダの Z 相入力です。機械原点復帰駆動の ORG 入力                            |

| 119        | 75     | EZ2                                 | T   | <b>T</b> # | と EZ 入力とで行う原点復帰動作では、ORG がアクティブ                             |

| 100        | -      | EZ3                                 | I   | 止貝         | になり減速を完了した後に EZ 入力がアクティブになれば                               |

| 81         | -      | EZ4                                 |     |            | 停止します。入力の感度は基準クロックの1周期のサンプ                                 |

|            |        |                                     |     |            | リングによるエッジ動作です。                                             |

| 144        | 100    | INP1                                |     |            | サーボドライバの位置決め完了入力です。初期設定レジス<br>タで位置決め完了で停止フラグ ON の設定のときは、パル |

| 123        | 79     | INP2                                | T   | <b>T</b> # | <u> </u>                                                   |

| 104        | -      | INP3                                | I   | 止貝         | ス出力完了後に INP 入力がアクティブになれば動作完了フラグが ON になります。正常原は割りみる場合も同様に   |

| 85         | -      | INP4                                |     |            | ラグが ON になります。正常停止割り込みの場合も同様に                               |

| 132        | 86     | MADIZI                              |     |            | INT 出力がアクティブになります。<br>センサ位置決めの開始入力です。センサ位置決め駆動のと           |

| 111        | 67     | $\frac{\text{MARK1}}{\text{MARK2}}$ |     |            | センサ位直決めの開始人力です。センサ位直決の駆動のと<br>き MARK 入力がアクティブになったところから設定パル |

| 92         | -      | MARK3                               | I   | 正負         | ス数を出力します。入力の感度は基準クロックの1または                                 |

| 73         | _      | MARK4                               |     |            |                                                            |

| 13         | _      | 14171717174                         |     |            | 16 周期です。                                                   |

表 1-2: 端子説明

| 端子番号   |        |            |     |            |                                           |

|--------|--------|------------|-----|------------|-------------------------------------------|

| X7043A | X7023A | 信号名        | I/O | 論理         | 内 容                                       |

| 45     | 43     |            |     |            |                                           |

| 44     | 42     | INO        |     |            |                                           |

| 43     | 41     | IN1<br>IN2 |     |            |                                           |

| 42     | 40     | IN3        |     |            | <br>IN0(LSB) から IN7(MSB) は 8 ビットパラレル入力です。 |

| 41     | 39     | IN4        | Ι   | 負          | <br>INOは High から Low の変化で割り込みができます。       |

| 40     | 36     | IN5        |     |            |                                           |

| 39     | 35     | IN6<br>IN7 |     |            |                                           |

| 38     | 34     | 1117       |     |            |                                           |

| 64     | 58     | CLRA1      |     |            | <br>CLRA が Low のときマルチカウンタ A は 0 にクリアされ    |

| 63     | 57     | CLRA2      | I   | 負          | ます。                                       |

| 62     | -      | CLRA3      | •   | 只          |                                           |

| 61     | -      | CLRA4      |     |            | レベル動作またはエッジ動作の切り替えができます。                  |

| 4      | 4      | POUT1      |     |            | 指令パルス出力です。2 パルス方式のときは CW 方向のパ             |

| 129    | 83     | POUT2      | O   | 正負         | ルス出力をします。パルス / 方向方式のときはパルス出力              |

| 108    | -      | POUT3      | O   | 止只         | をします。出力の論理は出力論理レジスタで切り替えがで                |

| 89     | -      | POUT4      |     |            | きます。                                      |

| 3      | 3      | PDIR1      |     |            | 方向出力または指令パルス出力です。2 パルス方式のときは              |

| 128    | 82     | PDIR2      | O   | 正負         | CCW 方向のパルス出力をします。パルス / 方向方式のとき            |

| 107    | -      | PDIR3      | O   | 正貝         | は方向出力をします。出力の論理は出力論理レジスタで切                |

| 88     | -      | PDIR4      |     |            | り替えができます。                                 |

| 1      | 1      | CLR1       |     |            | サーボドライバの偏差カウンタクリア用の1ショットまた                |

| 124    | 80     | CLR2       |     |            | は汎用出力です。1 ショットまたは汎用出力の切り替えは出              |

| 105    |        | CLR3       | О   | 正負         | 力の初期設定レジスタで行います。1 ショットのパルス幅は              |

| 86     | -      | CLR4       |     |            | 基準クロックの 32 周期です。出力の論理は出力論理レジス             |

| 80     | -      |            |     |            | タで切り替えができます。                              |

| 2      | 2      | SON1       |     |            |                                           |

| 125    | 81     | SON2       | 0   | <b>A</b>   | サーボドライバ用のサーボオン出力です。汎用出力として                |

| 106    | -      | SON3       | О   | 負          | 使用できます。                                   |

| 87     | -      | SON4       |     |            |                                           |

| 57     | 53     | OUT0       |     |            |                                           |

| 56     | 52     | OUT1       |     |            |                                           |

| 53     | 51     | OUT2       |     |            | OUT0(LSB)から OUT7(MSB)は 8 ビットパラレルの汎用出      |

| 52     | 50     | OUT3       |     | <b>F</b> . | カです。                                      |

| 51     | 49     | OUT4       | О   | 負          | 8 ビット同時の書換と各ビットごとのビットオペレーショ               |

| 50     | 48     | OUT5       |     |            | ンができます。                                   |

| 49     | 47     | OUT6       |     |            |                                           |

| 48     | 46     | OUT7       |     |            |                                           |

| 6      | 6      | ERROR1     |     |            | エラー停止モニタ出力です。ALM、+EL、-EL によるエラー停          |

| 131    | 85     | ERROR2     |     |            | 止のときに Low になります。停止フラグをリセットすると             |

| 110    | -      | ERROR3     | О   | 正負         | High になります。出力の論理は出力論理レジスタで切り替             |

| 91     | -      | ERROR4     |     |            |                                           |

| 91     | -      | EKKOK4     |     |            | えができます。                                   |

表 1-2: 端子説明

|           | 27 1 5 3H 1 DO21 |        |     |           |                                         |  |  |

|-----------|------------------|--------|-----|-----------|-----------------------------------------|--|--|

| 端子番号      |                  | 信号名    | I/O | 論理        | 内容                                      |  |  |

| X7043A    | X7023A           | 10.2.0 |     | MIII)     | r, 12                                   |  |  |

| 5         | 5                | MOVE1  |     |           | パルス出力中のモニタ出力です。パルス出力中は Low にな           |  |  |

| 130       | 84               | MOVE2  | 0   | <b>元名</b> |                                         |  |  |

| 109       | -                | MOVE3  | U   | 正貝        | ります。出力の論理は出力論理レジスタで切り替えができ              |  |  |

| 90        | -                | MOVE4  |     |           | ます。                                     |  |  |

| 142       | 98               | EA1    |     |           | │<br>│エンコーダ入力の A 相入力です。2 クロック方式と 90°位 │ |  |  |

| 121       | 77               | EA2    | I   | <b>A</b>  |                                         |  |  |

| 102       | -                | EA3    | 1   | 負         | 相差の1、2、4 逓倍の選択はエンコーダ入出力の初期設定で           |  |  |

| 83        | -                | EA4    |     |           | できます。                                   |  |  |

| 141       | 97               | EB1    |     |           | <br> エンコーダ入力の B 相入力です。2 クロック方式と 90°位    |  |  |

| 120       | 76               | EB2    | I   | 自         | 相差の1、2、4 逓倍の選択はエンコーダ入出力の初期設定で           |  |  |

| 101       | -                | EB3    | 1   | 貝         |                                         |  |  |

| 82        | -                | EB4    |     |           | できます。                                   |  |  |

| 37        | 33               | CMP1   |     |           | <br> コンパレータレジスタとカウンタ (A、B、C) またはカウンタ    |  |  |

| 36        | 32               | CMP2   | 0   | 負         | どうしの比較出力です。=または>の切り替えはコンパ               |  |  |

| 35        | -                | CMP3   |     |           | レータ制御レジスタで行います。                         |  |  |

| 34        | -                | CMP4   |     |           | ア と かい 関 アンベン  に 110・35 9 。             |  |  |

|           |                  |        |     |           | 同期スタート入力です。同期スタートモードのとき起動を              |  |  |

| 60        | 56               | SYNC   | I   | 負         | かけた後 SYNC が High から Low に変化すればパルス出力     |  |  |

|           |                  |        |     |           | を開始します。                                 |  |  |

|           |                  |        |     |           | 直線補間ステータス入出力です。本 LSI を複数個使用して           |  |  |

|           |                  |        |     |           | 直線補間を行うときに各 LSI の CP0、CP1、CP2、CP3 をそれ   |  |  |

|           |                  |        |     |           | ぞれワイヤードオアで接続します。出力バッファはオープ              |  |  |

| 72        | 66               | CP0    |     |           | ンドレインになっています。各端子の機能は次のように               |  |  |

| 71        | 65               | CP1    | I/O | <b>4</b>  | なっています。                                 |  |  |

| 70        | 64               | CP2    | 1/0 | 負         | 優先度                                     |  |  |

| 69        | 63               | CP3    |     |           |                                         |  |  |

|           |                  |        |     |           | 2 <u>CP1</u> 減速停止                       |  |  |

|           |                  |        |     |           | 3 CP2 定速                                |  |  |

|           |                  |        |     |           | 4 CP3 減速                                |  |  |

| 32,33,65, | 30,31,59,        |        |     |           | En 14 (4 1 ° )                          |  |  |

| 66,67,68  | 60,61,62         | NC     |     |           | 無接続ピンです。                                |  |  |

# 【注】 1.INT はオープンドレイン出力です。

2.ALM、+EL、-EL、+SLD、-SLD、ORG、EZ、INP、MARK、INO-7、EA、EB、SYNC、CLRA は プルアップ抵抗内蔵入力です。

3.CP0-3 はプルアップ抵抗内蔵入出力です。

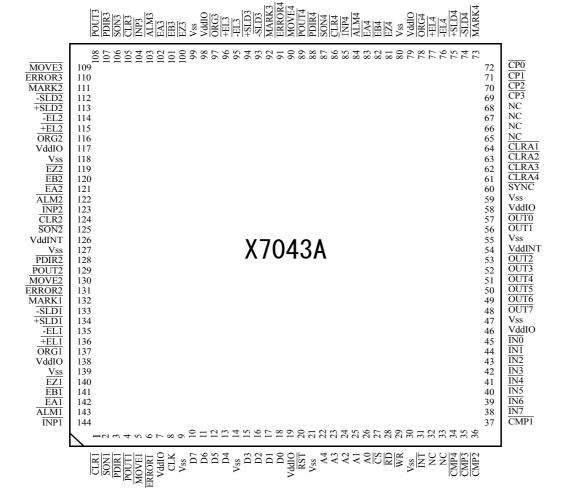

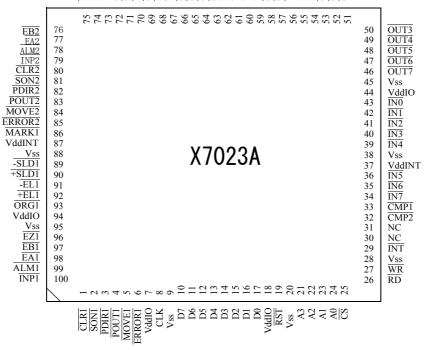

#### 1-6-2 ピン配置

図 1-4: ピン配置図

### 1-7 システムの構成

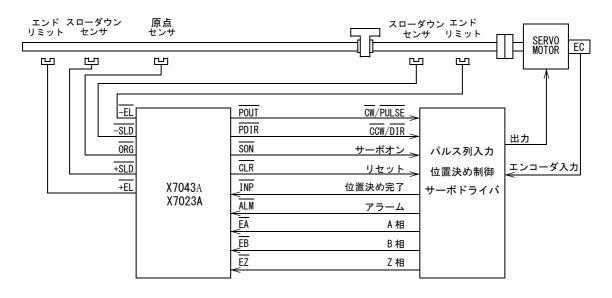

図 1-5: サーボモータインターフェース例

図 1-6: ステッピングモータインターフェース例

#### 1-8 CPU とのインターフェース例

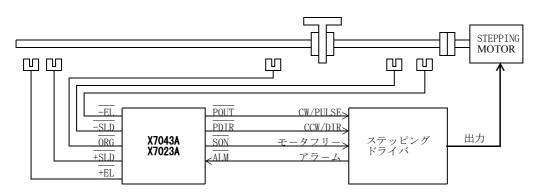

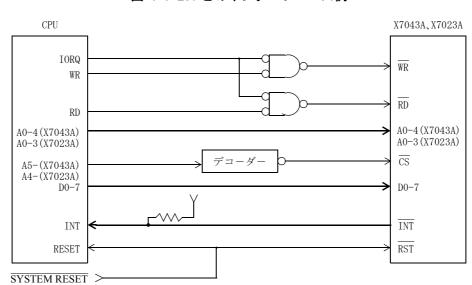

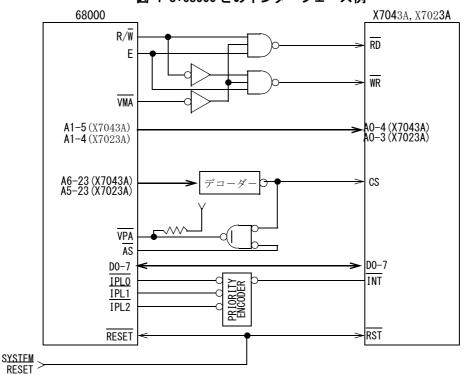

本 LSI では D0 ~ 7 の 8 ビットデータバスを介し 80 系プロセッサに直結可能なバスインターフェースを採用していますが、簡単な外付け回路を構成することにより 68 系プロセッサによってもインターフェースすることができます。

#### 1-8-1 Z80 とのインターフェース例

図 1-7: Z80 とのインターフェース例

#### 1-8-2 68000 とのインターフェース例

図 1-8:68000 とのインターフェース例

# 2. アドレス割付とデータのリード・ライト

#### 2-1 アドレス割付表

表 2-1: アドレス割付表

| A4 | A3 | A2  | A1    | A0  | WRITE                   | READ                    |  |  |  |  |  |

|----|----|-----|-------|-----|-------------------------|-------------------------|--|--|--|--|--|

| 0  | 0  | 0   | 0     | 0   | #1 軸レジスタセレクタ            | #1 軸レジスタセレクタ            |  |  |  |  |  |

| 0  | 0  | 0   | 0     | 1   | #1 軸書き込みデータ 1(bit0-7)   | #1 軸読み出しデータ 1(bit0-7)   |  |  |  |  |  |

| 0  | 0  | 0   | 1     | 0   | #1 軸書き込みデータ 2(bit8-15)  | #1 軸読み出しデータ 2(bit8-15)  |  |  |  |  |  |

| 0  | 0  | 0   | 1     | 1   | #1 軸書き込みデータ 3(bit16-23) | #1 軸読み出しデータ 3(bit16-23) |  |  |  |  |  |

| 0  | 0  | 1   | 0     | 0   | #1 軸書き込みデータ 4(bit24-31) | #1 軸読み出しデータ 4(bit24-31) |  |  |  |  |  |

| 0  | 0  | 1   | 0     | 1   | システム予約(アクセス禁止)          | 割込み軸ステータス               |  |  |  |  |  |

| 0  | 0  | 1   | 1     | 0   | システム予約(アクセス禁止)          | #1 軸割り込み状態ステータス         |  |  |  |  |  |

| 0  | 0  | 1   | 1     | 1   | #1 軸コマンド                | #1 軸動作状態ステータス           |  |  |  |  |  |

| 0  | 1  | 000 | b ~ 1 | 11b | #2 軸アクセス領域 #1 軸と同一割り    | 当て                      |  |  |  |  |  |

| 1  | 0  | 000 | b ~ 1 | 11b | #3 軸アクセス領域 #1 軸と同一割り当て  |                         |  |  |  |  |  |

| 1  | 1  | 000 | b ~ 1 | 11b | #4 軸アクセス領域 #1 軸と同一割り    | 当て                      |  |  |  |  |  |

【注】 1. WRITE サイクルでは、データの書き込み処理に基準クロックの2周期の時間(リカバリタイム) を要します。

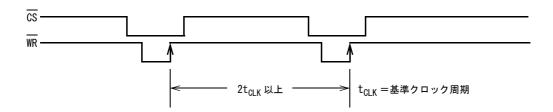

図 2-1:WRITE サイクルとリカバリタイム

- 2. コマンドの書き込み、割り込み状態モニタと動作状態モニタ以外のパラメータ、カウンタ初期 設定は、レジスタセレクタを設定した後に書き込みデータ1~4、読み出しデータ1~4でリー ド・ライトします。

- 3. 書き込みデータが 2 バイト以上の場合は、下位から上位の順に書き込みます。最上位書き込み 時に一括に取り込みがされます。

- 4. 読み出しデータが2バイト以上の場合は、レジスタセレクタをライトした後に読み出します。 レジスタセレクタの書き込み時に一括読み出し用補助バッファにデータがラッチされます。 読み出しは連続して行います。

# 3. コマンドの種類と機能

# 3-1 コマンドのライト

コマンドレジスタに1バイトの命令コードをライトします。

# 3-2 コマンド一覧

表 3-1: コマンド一覧

| 命令コード (16 進) | 種類                 | 説明                                                                  |  |  |

|--------------|--------------------|---------------------------------------------------------------------|--|--|

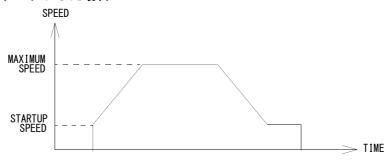

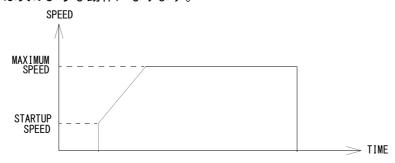

| 00h          | インデックス駆動(+方向)      | 加減速を伴った位置決め駆動です  SPEED  MAXIMUM SPEED /                             |  |  |

| 01h          | インデックス駆動(一方向)      | STARTUP SPEED DECELERATION POINT                                    |  |  |

| 02h          | 定速インデックス駆動(+方向)    | 起動時の速度での位置決め駆動です SPEED ↑                                            |  |  |

| 03h          | 定速インデックス駆動(一方向)    | STARTUP > TIME                                                      |  |  |

| 06h          | 連続駆動(十方向)          | 加速を伴った連続パルス駆動です。即時停止命令(コマンド 30h)または減速停止命令(コマンド 31h)をラ               |  |  |

| 07h          | 連続駆動(一方向)          | イトするか、+EL、-EL または ALM がアクティブになるまでパルスを出力します。                         |  |  |

| 08h          | 定速連続駆動(十方向)        | 起動時の速度での連続パルス駆動です。即時停止命令(コマンド 30h)または減速停止命令(コマンド                    |  |  |

| 09h          | 定速連続駆動(一方向)        | 31h)をライトするか、+EL、-EL または ALM がアクティブになるまでパルスを出力します。                   |  |  |

| 0Ah          | センサ位置決め駆動 I( 十方向 ) | MARK 入力端子がアクティブになった位置からの位置決め駆動です。駆動の最初から加速を行います。SPEED MAXIMUM SPEED |  |  |

| 0Bh          | センサ位置決め駆動 I( 一方向)  | STARTUP DECELERATION POINT TIME                                     |  |  |

| 命令コード<br>(16 進) | 種 類                | 説明                                                                               |

|-----------------|--------------------|----------------------------------------------------------------------------------|

| 0Ch             | センサ位置決め駆動 II (+方向) | MARK 入力端子がアクティブになった位置からの位置決め駆動です。加速は MARK 入力がアクティブになってから行います。  SPEED  MAXIMUM    |

| 0Dh             | センサ位置決め駆動 II (一方向) | STARTUP SPEED DECELERATION POINT TIME                                            |

| 0Eh             | センサ位置決め駆動皿(+方向)    | MARK 入力端子がアクティブになった位置からの位置決め駆動です。加減速は行いません。 SPEED                                |

| 0Fh             | センサ位置決め駆動皿(一方向)    | STARTUP SPEED - TIME                                                             |

| 12h             | 原点復帰 I (+方向)       | 加減速を伴った原点復帰です。ORG がアクティブに<br>なると減速停止します。<br>SPEED  MAXIMUM                       |

| 13h             | 原点復帰 I (一方向)       | STARTUP SPEED TIME                                                               |

| 14h             | 原点復帰Ⅱ(+方向)         | 加減速を伴った原点復帰です。ORGがアクティブになると減速し、起動速度になった後EZがアクティブになると停止します。  SPEED  MAXIMUM SPEED |

| 15h             | 原点復帰Ⅱ(一方向)         | STARTUP SPEED TIME ORG                                                           |

| 命令コード | 種類         | 説明                                                                                                              |

|-------|------------|-----------------------------------------------------------------------------------------------------------------|

| (16進) | IE //K     | .,,                                                                                                             |

| 16h   | 原点復帰皿(十方向) | 起動時の速度での原点復帰です。ORG がアクティブになると即時停止します。 SPEED                                                                     |

| 17h   | 原点復帰皿(一方向) | STARTUP                                                                                                         |

| 18h   | 原点復帰Ⅳ(十方向) | 起動時の速度での原点復帰です。ORG がアクティブになった後、EZ がアクティブになると即時停止します。 SPEED                                                      |

| 19h   | 原点復帰Ⅳ(一方向) | STARTUP SPEED TIME  ORG  EZ                                                                                     |

| 1Ah   | 原点復帰V(+方向) | 加減速を伴った原点復帰です。ORG がアクティブになると減速し EZ 入力による割り込みがイネーブルになります。原点復帰 II 命令を行うと次の EZ がアクティブになったエッジで停止します。  MAXIMUM PREED |

| 1Bh   | 原点復帰Ⅴ(一方向) | STARTUP SPEED TIME  INT  ORG  EZ                                                                                |

| 30h   | 即時停止命令     | 駆動中にこの命令をライトすると即時停止します。<br>最終パルスのパルス幅は確保します。補間モードの<br>ときは 1 軸のみの停止になります。                                        |

| 31h   | 減速停止命令     | 駆動中にこの命令をライトすると減速停止します。<br>定速駆動中のときは即時停止になります。最終パルスのパルス幅は確保します。補間モードのときは他の軸も同時に減速停止します。                         |

| 命令コード | 種類                         | 説明                                                                                                                                                |

|-------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| (16進) | 1年 スス                      | נקי אם                                                                                                                                            |

| 32h   | 減速命令                       | 加減速を伴った駆動中にこの命令をライトすると起動時の速度まで減速します。補間モードのときは他の軸も同時に減速します。                                                                                        |

| 33h   | 減速解除命令                     | 減速命令の後にこの命令をライトすると最高速まで<br>加速します。補間モードのときは他の軸も同時に減<br>速解除します。                                                                                     |

| 34h   | 定速命令                       | 加減速を伴った駆動中にこの命令をライトすると現在の速度に固定されます。補間モードのときは他の軸も同時に現在の速度に固定されます。                                                                                  |

| 35h   | 定速解除命令                     | 定速の駆動命令中または定速命令後にこの命令をライトすると再び加減速の動作がはじまります。補間<br>モードのときは他の軸も同時に再び加減速の動作が<br>始まります。                                                               |

| 36h   | 一斉停止命令                     | 補間モードのときにこの命令をすると全軸が一斉停止します。                                                                                                                      |

| 40h   | タイマ動作 I                    | パルスを出力しないインデックス駆動です。                                                                                                                              |

| 41h   | タイマ動作Ⅱ                     | パルスを出力しない定速インデックス駆動です。                                                                                                                            |

| 50h   | カウンタ A のクリア命令              | カウンタ A を 0 にクリアします。                                                                                                                               |

| 51h   | カウンタ B のクリア命令              | カウンタ B を 0 にクリアします。                                                                                                                               |

| A0h   | 動作完了フラグリセット命令              | 動作完了フラグが立っているときにこの命令をライトするとフラグがリセットされます。動作完了フラグおよびエラーフラグが立っているときも、この命令によりフラグがリセットされます。動作完了フラグが立っているときは、駆動命令をライトしても再起動されませんので必ずこの命令でリセットする必要があります。 |

| A2h   | 減速開始割り込みフラグリセット命令          | 減速開始割り込みフラグが立っているときに、この<br>命令をライトすると減速開始割り込みフラグがリ<br>セットされます。                                                                                     |

| A3h   | 等速度割り込みフラグリセット命令           | 等速度割り込みフラグが立っているときに、この命令をライトすると等速度割り込みフラグがリセットされます。                                                                                               |

| A5h   | 最大加速度割り込みフラグリセット命<br>令     | 最大加速度割り込みフラグが立っているときに、こ<br>の命令をライトすると最大加速度割り込みフラグが<br>リセットされます                                                                                    |

| A8h   | カウンタ A キャリー割り込みフラグリ<br>セット | カウンタ A のキャリー割り込みフラグが立っている<br>ときに、この命令をライトするとカウンタ A のキャ<br>リー割り込みフラグがリセットされます。                                                                     |

| A9h   | カウンタ A ボロー割り込みフラグリ<br>セット  | カウンタ A のボロー割り込みフラグが立っているときに、この命令をライトするとカウンタ A のボロー割り込みフラグがリセットされます。                                                                               |

| 命令コード<br>(16 進) | 種類                           | 説明                                                                                     |

|-----------------|------------------------------|----------------------------------------------------------------------------------------|

| AAh             | カウンタ B キャリー割り込みフラグリ<br>セット   | カウンタ B のキャリー割り込みフラグが立っている<br>ときに、この命令をライトするとカウンタ B のキャ<br>リー割り込みフラグがリセットされます。          |

| ABh             | カウンタ B ボロー割り込みフラグリ<br>セット    | カウンタ B のボロー割り込みフラグが立っているときに、この命令をライトするとカウンタ B のボロー割り込みフラグがリセットされます。                    |

| ADh             | カウンタ C ボロー割り込みフラグリ<br>セット    | カウンタ C のボロー割り込みフラグが立っているときに、この命令をライトするとカウンタ C のボロー割り込みフラグがリセットされます。                    |

| B0h             | <br>ORG センサ割り込みフラグリセット       | ORG センサ割り込みフラグが立っているときに、この命令をライトすると ORG センサ割り込みフラグがリセットされます。                           |

| Blh             | <br>EZ センサ割り込みフラグリセット        | EZ センサ割り込みフラグが立っているときに、この<br>命令をライトすると EZ センサ割り込みフラグがリ<br>セットされます。                     |

| B2h             | <br>INO 入力割り込みフラグリセット        | NO   入力割り込みフラグが立っているときに、この命令をライトすると   NO   割り込みフラグがリセットされます。                           |

| B3h             | <br>MARK 入力割り込みフラグリセット       | MARK 入力割り込みフラグが立っているときに、この命令をライトすると MARK センサ割り込みフラグがリセットされます。                          |

| B8h             | コンパレータ(P = Q)割り込みフラグリセット     | コンパレータ $(P = Q)$ による割り込みフラグが立っているときに、この命令をライトするとコンパレータ $(P = Q)$ 割り込みフラグがリセットされます。     |

| B9h             | コンパレータ(P > Q)割り込みフラグリ<br>セット | コンパレータ $(P > Q)$ による割り込みフラグが立っ<br>ているときに、この命令をライトするとコンパレータ $(P > Q)$ 割り込みフラグがリセットされます。 |

| E0h             | OUT0 をセット                    |                                                                                        |

| E1h             | OUT1 をセット                    |                                                                                        |

| E2h             | OUT2 をセット                    |                                                                                        |

| E3h             | OUT3 をセット                    | 汎用出力のビットオペレーションです。OUT0 ~ 7 の                                                           |

| E4h             | OUT4 をセット                    | それぞれの端子を Low にします。                                                                     |

| E5h             | OUT5 をセット                    |                                                                                        |

| E6h             | OUT6 をセット                    |                                                                                        |

| E7h             | OUT7 をセット                    |                                                                                        |

| EEh             | SON をセット                     | サーボ ON 用出力端子 SON を Low にします。                                                           |

| 命令コード<br>(16 進 ) | 種類          | 説明                                                                 |

|------------------|-------------|--------------------------------------------------------------------|

| EFh              | <br>CLR を出力 | 1 ショットの設定のときは CLR 端子から基準クロックの 32 周期のパルスを出力します。汎用入力の設定のときは ON にします。 |

| F0h              | OUT0 をリセット  |                                                                    |

| F1h              | OUT1 をリセット  |                                                                    |

| F2h              | OUT2 をリセット  |                                                                    |

| F3h              | OUT3 をリセット  | 汎用出力のビットオペレーションです。OUT0 ~ 7 の                                       |

| F4h              | OUT4 をリセット  | それぞれの端子を High にします。                                                |

| F5h              | OUT5 をリセット  |                                                                    |

| F6h              | OUT6 をリセット  |                                                                    |

| F7h              | OUT7 をリセット  |                                                                    |

| FEh              | SON をリセット   | サーボ ON 用出力端子 SON を High にします。                                      |

| FFh              | CLR をリセット   | 汎用入力の設定のときは CLR を OFF にします。                                        |

# 4. 各種レジシタと内部カウンタについて

# 4-1 レジスタとカウンタの一覧

表 4-1: レジスタ及びカウンター覧

| セレクトコード<br>16 進 | レジスタ・カウンタ                            | 有 効<br>ビット長 | 設定範囲                                        | 種別    | 上位アドレスの<br>リード・ライト数 |

|-----------------|--------------------------------------|-------------|---------------------------------------------|-------|---------------------|

| 00h             | 周波数数倍率設定レジスタ(R <sub>0</sub> )        | 12          | 1 ~ 4,096                                   | パラメータ | 2 バイトー括 RW          |

| 01h             | 出力パルス数設定レジスタ (カウンタ C/R₁)             | 24          | 0 ~ 16,777,215                              | パラメータ | 3 バイトー括 RW          |

| 02h             | 減速開始点設定レジスタ (カウンタ D/R <sub>2</sub> ) | 24          | 0 ~ 16,777,215<br>-8,388,608 ~<br>8,388,607 | パラメータ | 3 バイト一括 RW          |

| 03h             | 起動周波数設定レジスタ (R <sub>3</sub> )        | 14          | 1 ~ 16,383 *1<br>1 ~ 10,000 *2              | パラメータ | 2 バイトー括 RW          |

| 04h             | 最高周波数設定レジスタ (R <sub>4</sub> )        | 14          | 1 ~ 16,383 *1<br>1 ~ 10,000 *2              | パラメータ | 2 バイトー括 RW          |

| 05h             | 加速レート設定レジスタ(R <sub>5</sub> )         | 14          | 1 ~ 16,383                                  | パラメータ | 2 バイトー括 RW          |

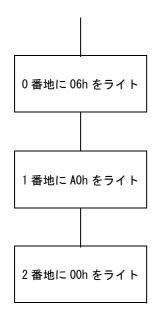

| 06h             | 減速レート設定レジスタ(R <sub>6</sub> )         | 14          | 1 ~ 16,383                                  | パラメータ | 2 バイトー括 RW          |

| 07h             | S 字加減速区間設定レジスタ(R <sub>7</sub> )      | 13          | 1 ~ 8,191                                   | パラメータ | 2 バイトー括 RW          |

| 08h             | 直線補間基数設定レジスタ(Rg)                     | 24          | 1 ~ 16,777,215                              | パラメータ | 3 バイトー括 RW          |

| 21h             | カウンタ A                               | 24/32       | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,         | カウンタ  | 3/4 バイトー括 RW        |

| 22h             | カウンタ B                               | 24/32       |                                             | カウンタ  | 3/4 バイトー括 RW        |

| 23h             | 周波数読み出し                              | 14          |                                             | 周波数   | 2 バイトー括 RD          |

| 30h             | コンパレータレジスタ                           | 24          | 0 ~ 16,777,215<br>-8,388,608 ~<br>8,388,607 |       | 3 バイト一括 RW          |

| 40h             | 汎用出力一括設定(OUTO ~ 7)                   | 8           |                                             | I/O   | 1バイト RW             |

| 50h             | パルス出力初期設定レジスタ                        | 4           |                                             | 初期設定  | 1バイト RW             |

| 51h             | エンコーダ入出力初期設定レジスタ                     | 2           |                                             | 初期設定  | 1バイト RW             |

| 52h             | カウンタ A 初期設定レジスタ                      | 5           |                                             | 初期設定  | 1バイト RW             |

| 53h             | カウンタ B 初期設定レジスタ                      | 7           |                                             | 初期設定  | 1バイト RW             |

| 54h             | 入力の初期設定レジスタ                          | 5           |                                             | 初期設定  | 1バイト RW             |

| 55h             | 入力論理の初期設定レジスタ                        | 9           |                                             | 初期設定  | 2 バイト個別 RW          |

| 56h             | 入力フィルタの初期設定レジスタ(F)                   | 8           |                                             | 初期設定  | 1バイト RW             |

| 57h             | 出力の初期設定レジスタ                          | 1           |                                             | 初期設定  | 1バイト RW             |

| 58h             | 出力論理の初期設定レジスタ                        | 6           |                                             | 初期設定  | 1バイト RW             |

| 60h             | 動作制御モード設定レジスタ                        | 6           |                                             | 制御モード | 1バイト RW             |

| 61h             | カウンタ A 制御モード設定レジスタ                   | 2           |                                             | 制御モード | 1バイト RW             |

| 62h             | カウンタ B 制御モード設定レジスタ                   | 2           |                                             | 制御モード | 1バイト RW             |

| 63h             | CLR 出力制御モード設定レジスタ                    | 2           |                                             | 制御モード | 1バイト RW             |

| 64h             | コンパレータ制御モード設定レジスタ                    | 6           |                                             | 制御モード | 1バイト RW             |

| 70h             | パルス発振割り込みマスクレジスタ                     | 5           |                                             | 割り込み  | 1バイト RW             |

| 71h             | カウンタ割り込みマスクレジスタ                      | 5           |                                             | 割り込み  | 1バイト RW             |

| 72h             | センサ割り込みマスクレジスタ                       | 4           |                                             | 割り込み  | 1バイト RW             |

| 73h             | コンパレータ割り込みマスクレジスタ                    | 2           |                                             | 割り込み  | 1バイト RW             |

| E0h             | パルス発振割り込みフラグレジスタ                     | 5           |                                             | 割り込み  | 1バイト RD             |

| E1h             | カウンタ割り込みフラグレジスタ                      | 5           |                                             | 割り込み  | 1バイト RD             |

| E2h             | センサ割り込みフラグレジスタ                       | 4           |                                             | 割り込み  | 1バイト RD             |

| E3h             | コンパレータ割り込みフラグレジスタ                    | 2           |                                             | 割り込み  | 1バイト RD             |

| F0h             | センサ状態ステータスレジスタ                       | 9           |                                             | ステータス | 2 バイト個別 RD          |

| F1h             | 正常停止要因ステータスレジスタ                      | 4           |                                             | ステータス | 1バイト RD             |

| F2h             | エラー停止要因ステータスレジスタ                     | 3           |                                             | ステータス | 1バイト RD             |

| F3h             | 汎用入力状態ステータスレジスタ                      | 8           |                                             | ステータス | 1バイト RD             |

| F4h             | コンパレータ状態ステータスレジスタ                    | 2           |                                             | ステータス | 1バイト RD             |

$<sup>^{*1}</sup>$ : 直線加減速モードまたは減速開始点マニュアル設定モード。  $^{*2}$ :S 字加減速モードかつ減速開始点自動算出モード。 RW: リードおよびライト RD: リードのみ

#### 4-2 レジスタとカウンタのリード・ライト

表 4-1 のレジスタとカウンタのリード・ライトは、表 2-1 アドレス割付表のレジスタセレクタにセ レクトコードをライトし、データ1~4をリードまたはライトして行います。

#### 4-2-1 1バイトのレジスタのリードとライト

リードはレジスタセレクタにセレクトコードをライトし、読み出しデータ1をリードします。 ライトはレジスタセレクタにセレクトコードをライトし、書き込みデータ1にライトします。

#### 4-2-2 2 バイトのレジスタのリードとライト

リードはレジスタセレクタにセレクトコードをライトし、読み出しデータ1で下位のバイト(0~ 7bit) をリードし、その後読み出しデータ2で上位のバイト(8~15bit)をリードします。

ライトはレジスタセレクタにセレクトコードをライトし、書き込みデータ1で下位のバイト(0~ 7bit) をライトし、その後書き込みデータ2で上位のバイト(8~15bit) をライトします。

#### 4-2-3 3 バイトのレジスタとカウンタのリードとライト

リードはレジスタセレクタにセレクトコードをライトし、読み出しデータ1で下位のバイト(0~ 7bit)をリードし、次に読み出しデータ2で中位のバイト(8~15bit)をリードし、その後読み出しデー タ3で上位のバイト(16~23bit)をリードします。

ライトはレジスタセレクタにセレクトコードをライトし、書き込みデータ1で下位のバイト(0~ 7bit)をライトし、次に書き込みデータ2で中位にバイト(8~15bit)をライトし、その後書き込みデー タ 3 で上位のバイト(16 ~ 23bit)をライトします。

#### 4-2-4 4バイトのカウンタのリードとライト

リードはレジスタセレクタにセレクトコードをライトし、読み出しデータ1で下位のバイト(0~ 7bit) をリードし、次に読み出しデータ 2 で中位のバイト(8 ~ 15bit) をリードし、次に読み出しデー タ 3 で次の中位バイト(16 ~ 23bit)をリードし、最後に読み出しデータ 4 で最上位のバイト(24 ~ 31bit)をリードします。

ライトはレジスタセレクタにセレクトコードをライトし、書き込みデータ1で下位のバイト(0~ 7bit)をライトし、次に書き込みデータ2に中位のバイト(8~15bit)をライトし、次に書き込みデー タ3で次の中位のバイト(16~23bit)をライトし、最後に書き込みデータ4に最上位のバイト(24~ 31bit) をライトします。

### 5. パルス出力に関する各パラメータについて

本 LSI でパルス出力やタイマ動作の為に 9 種類のパラメータがあります。 このパラメータは  $R_0$  から  $R_8$  のパラメータレジスタにより設定します。

#### 5-1 パラメータの種類

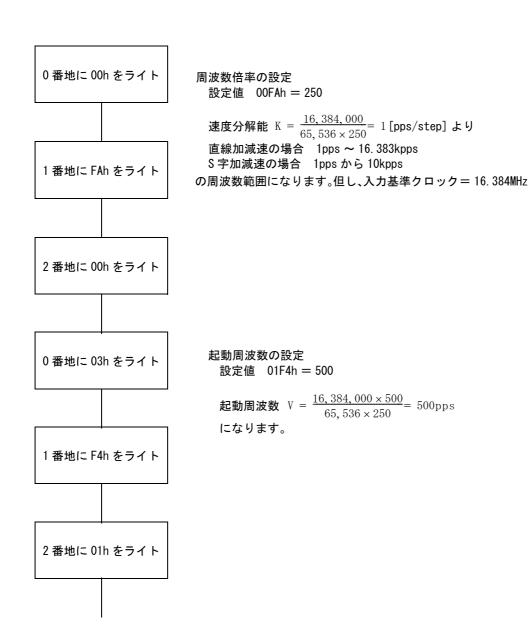

#### 5-1-1 周波数倍率設定レジスタ (R<sub>0</sub> レジスタ)

R<sub>0</sub>レジスタは出力周波数の倍率レンジを設定するレジスタです。

設定の範囲は1~4,096ですが、4096の場合は0を設定します。

R<sub>0</sub> レジスタの設定値と倍率[pps/step]および出力周波数の範囲は、表 5-1 のようになります。

| $R_0$ | 倍率[pps/step] | 出力周波数範囲[pps]           |                   |  |

|-------|--------------|------------------------|-------------------|--|

| IX()  |              | 直線加減速                  | S字加減速             |  |

| 2500  | 0.1          | 0.1 ~ 1,638.3          | 0.1 ~ 1,000       |  |

| 250   | 1            | 1 ~ 16,383             | 1 ~ 10,000        |  |

| 50    | 5            | 5 <b>~</b> 81,915      | 5 <b>~</b> 50,000 |  |

| 10    | 25           | 25 <b>~</b> 409,575    | 25 ~ 250,000      |  |

| 1     | 250          | 250 <b>~</b> 4,095,750 | 250 ~ 2,500,000   |  |

表 5-1: 周波数倍率と出力周波数範囲(基準クロック f=16.384MHz の場合)

#### 5-1-2 出力パルス数設定レジスタ (R<sub>1</sub> レジスタ)

R<sub>1</sub> レジスタは出力パルス数を設定するレジスタです。R<sub>1</sub> レジスタは、カウンタ C と共用しています。従って R<sub>1</sub> レジスタのライトは、カウンタ C のプリセットとなります。パルス出力を途中で強制的に停止したときのカウンタ C の値は、(R<sub>1</sub> レジスタ設定値ー出力パルス数)になっています。次回に残りパルス数のみを出力する場合は再設定をする必要がありません。その他の場合は毎回 R<sub>1</sub> レジスタの設定が必要です。

#### 5-1-3 減速開始点設定レジスタ (R<sub>2</sub> レジスタ)

本 LSI では減速開始点の自動算出モードを備えていますが、減速開始点のマニュアル設定や減速開始点のオフセット設定が  $R_2$  レジスタにデータをライトすることで行えます。

$R_2$  レジスタはカウンタ D と共用していますが、減速開始点マニュアル設定モードで使用するときはカウント動作を行いません。

#### 5-1-4 起動周波数設定レジスタ (R<sub>3</sub> レジスタ)

パルス出力開始時と終了時の周波数を決めるパラメータレジスタです。

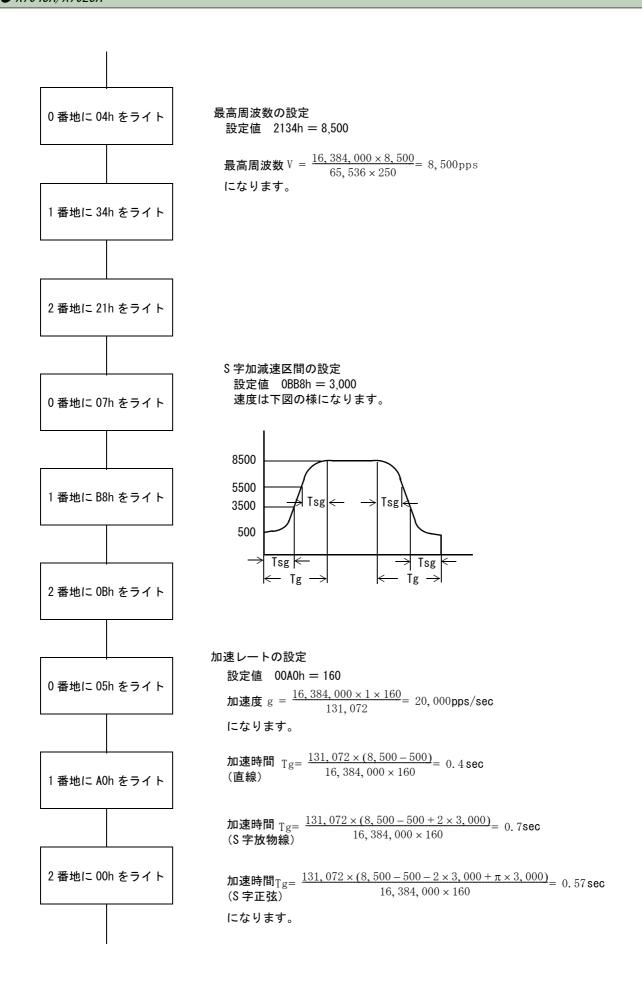

#### 5-1-5 最高周波数設定レジスタ (R<sub>4</sub> レジスタ)

パルス出力の最高周波数を決めるパラメータレジスタです。直線加減速かつ減速開始点自動算出モードではパルス出力中にも書換ができます。S字加減速の場合は連続モード及び減速開始点マニュアル設定モードでは等速パルス出力中であれば途中書換ができます。

#### 5-1-6 加速レート設定レジスタ (R<sub>5</sub> レジスタ)

加速度を決めるパラメータレジスタです。

### 5-1-7 減速レート設定レジスタ (R<sub>6</sub> レジスタ)

減速度を決めるパラメータレジスタです。

減速開始点自動算出モードでは  $R_5$  レジスタと  $R_6$  レジスタは、同じ値を設定して下さい。

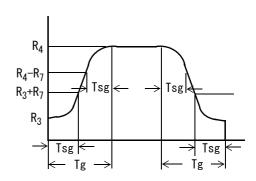

### 5-1-8 S字加減速区間設定レジスタ (R<sub>7</sub> レジスタ)

S字加減速区間とは図5-1に示すTsgの区間です。

$R_3$  からから  $(R_3+R_7)$  の速度区間と  $(R_4-R_7)$  から  $R_4$  の速度区間が S 字状に速度が変化します。  $R_7$  レジスタの設定値は $(R_4-R_3) \div 2$  以下になります。

S字加減速を使用しないときは、設定の必要はありません。

### 5-1-9 直線補間基数設定レジスタ (Rg レジスタ)

複数軸または本 LSI を複数個使用して直線補間駆動を 行うときに最も移動量の多い軸の R<sub>1</sub> レジスタ設定値を R<sub>8</sub> レジスタに設定します。

直線補間駆動を使用しないときは、設定の必要はありませ ん。

#### 図 5-1:8 字加減速の状態

# 5-2 パラメータの計算式

表 5-2: パラメータ計算式一覧

|                          | 役 0−2・ハファーテ計算式一見                                                                                                                                                                           |  |  |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 速度分解能[倍率]<br>K[pps/step] | $K = \frac{f}{65,536 \times R_0}$ f: 基準クロック周波数 [Hz]                                                                                                                                        |  |  |

| 起動周波数<br>V[pps]          | 単独モード $V=\frac{f\times R_3}{65,536\times R_0}$ 直線補間モード $V=\frac{f\times R_3\times R_1}{65,536\times R_0\times R_8}$                                                                        |  |  |

| 最高周波数<br>V[pps]          | 単独モード $V = \frac{f \times R_4}{65,536 \times R_0}$ 直線補間モード $V = \frac{f \times R_4 \times R_1}{65,536 \times R_0 \times R_8}$                                                              |  |  |

| 加速度<br>g[pps/sec]        | 単独モード $g = \frac{f \times K \times R_5}{131,072}$ 直線補間モード $g = \frac{f \times K \times R_5 \times R_1}{131,072 \times R_8}$                                                                |  |  |

| 減速度<br>g[pps/sec]        | 単独モード $g = \frac{f \times K \times R_6}{131,072}$ 直線補間モード $g = \frac{f \times K \times R_6 \times R_1}{131,072 \times R_8}$                                                                |  |  |

| 加減速時間(直線)<br>Tg[sec]     | (加速) $Tg = \frac{131,072 \times (R_4 - R_3)}{f \times R_5}$ (減速) $Tg = \frac{131,072 \times (R_4 - R_3)}{f \times R_6}$                                                                    |  |  |

| 加減速時間(正弦)<br>Tg[sec]     | (加速) $Tg = \frac{131,072 \times (R_4 - R_3 - 2 \times R_7 + \pi \times R_7)}{f \times R_5}$<br>(減速) $Tg = \frac{131,072 \times (R_4 - R_3 - 2 \times R_7 + \pi \times R_7)}{f \times R_6}$ |  |  |

| 加減速時間(放物線)<br>Tg[sec]    | (加速) $T_g = \frac{131,072 \times (R_4 - R_3 + 2 \times R_7)}{f \times R_5}$ (減速) $T_g = \frac{131,072 \times (R_4 - R_3 + 2 \times R_7)}{f \times R_6}$                                    |  |  |

| 減速開始点(直線)<br>Dp[ パルス ]   | 台形 $(R_4>R_3$ の場合) $Dp = \frac{(R_4-R_3)(R_4+R_3-1)}{R_0\times R_6}$ 三角駆動 $Dp = \frac{R_1\times R_5}{R_5+R_6}$                                                                             |  |  |

| 減速開始点(正弦)<br>Dp[ パルス ]   | 台形 $(R_4>R_3$ の場合) $Dp = \frac{(R_4-R_3-2\times R_7+\pi\times R_7)(R_4+R_3)}{R_0\times R_6}$ 三角駆動 $Dp = \frac{R_1\times R_5}{R_5+R_6}$                                                     |  |  |

| 減速開始点(放物線)<br>Dp[ パルス ]  | 台形 $(R_4 > R_3 $ の場合) $Dp = \frac{(R_4 - R_3 + 2 \times R_7 - 2)(R_4 + R_3)}{R_0 \times R_6}$ 三角駆動 $Dp = \frac{R_1 \times R_5}{R_5 + R_6}$                                                 |  |  |

#### π 円周率

# 6. 初期設定レジスタについて

初期設定レジスタはパワーオンリセット後に必ず1度設定をします。 その後パルス出力停止中には設定を替えることができます。

### 6-1 各初期設定レジスタの機能

#### 6-1-1 パルス出力初期設定レジスタ

表 6-1: パルス出力初期設定レジスタ

| bit | 内                  | 容                 |  |

|-----|--------------------|-------------------|--|

| DIC | 0                  | 1                 |  |

| 0   | 0.5 パルスアイドリング      | 1.5 パルスアイドリング     |  |

| 1   | 未定義(0を設定)          |                   |  |

| 2   | + 方向が CW パルス出力     | + 方向が CCW パルス出力   |  |

| 3   | CW、CCW の 2 クロック方式  | PULSE、DIR のゲート方式  |  |

| 4   | 未定義(0を設定)          |                   |  |

| 5   | 未定義(0を設定)          |                   |  |

| 6   | 未定義(0を設定)          |                   |  |

| 7   | パルス出力完了で動作完了フラグ ON | 位置決め完了で動作完了フラグ ON |  |

#### アイドリング

アイドリングとは加減速を遅らせる機能です。

設定が 0 のときは起動から 0.5 パルス後に加速が始まり、パルス停止の 0.5 パルス前に減速が終了します。設定が 1 のときは起動から 1.5 パルス後に加速が始まり、パルス停止の 1.5 パルス前に減速が終了します。

#### POUT、PDIR 出力

表 6-2: パルス出力初期設定と POUT と PDIR 出力

| bit3 | bit3 bit2 |   | UT | PDIR |   |

|------|-----------|---|----|------|---|

| DIG  | DILZ      | + | _  | +    | _ |

| 0    | 0         |   | Н  | Н    |   |

| 0    | 1         | н |    |      | н |

| 1    | 0         |   |    | Н    | L |

| 1    | 1         |   |    | L    | Н |

【注】 正論理の場合は反転します。

#### 動作完了フラグ

動作完了フラグは、動作状態ステータスでリードできます。

bit7=0 の時は、パルス出力完了後直ちに動作完了フラグは1になります。

bit7=1 の時は、パルス出力完了後 INP 入力端子がアクティブになれば1になります。

#### 6-1-2 エンコーダ入出力の初期設定レジスタ

表 6-3: エンコーダ入出力の初期設定レジスタ

| bit | 内                | 容 |  |

|-----|------------------|---|--|

| DIC | 0                | 1 |  |

| 0   | EA、EB 入力モードコード 1 |   |  |

| 1   | EA、EB 入力モードコード 2 |   |  |

| 2   | 未定義 (0 を設定 )     |   |  |

| 3   | 未定義 (0 を設定 )     |   |  |

| 4   | 未定義 (0 を設定 )     |   |  |

| 5   | 未定義 (0 を設定 )     |   |  |

| 6   | 未定義 (0 を設定 )     |   |  |

| 7   | 未定義(0を設定)        |   |  |

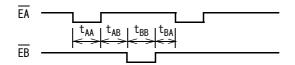

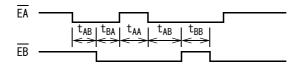

#### エンコーダ入力コード

表 6-4: エンコーダ入力モードコード

| コード 2 | コード 1 | 内 容          |

|-------|-------|--------------|

| 0     | 0     | 2 クロック負論理    |

| 0     | 1     | 2 相クロック 4 逓倍 |

| 1     | 0     | 2 相クロック 2 逓倍 |

| 1     | 1     | 2 相クロック 1 逓倍 |

#### 6-1-3 カウンタ A、B 初期設定レジスタ

表 6-5: カウンタ A、B 初期設定レジスタ

| bit | 内                            | 容                 |

|-----|------------------------------|-------------------|

| Dit | 0                            | 1                 |

| 0   | 内部発振パルスカウントディセーブル            | 内部発振パルスカウントイネーブル  |

| 1   | エンコーダカウントディセーブル              | エンコーダカウントイネーブル    |

| 2   | 未定義(0を設定)                    |                   |

| 3   | エンコーダ入力正カウント                 | エンコーダ入力逆カウント      |

| 4   | 未定義(0を設定)                    |                   |

| 5   | -8,388,608 ~ 8,388,607 のカウント | 0~16,777,215のカウント |

| 6   | 24bit モード                    | 32bit モード         |

| 7   | 未定義(0を設定)                    |                   |

#### 多重入力カウント

カウンタ A および B は、内部発振パルスとエンコーダ入力を同時カウント可能です。 bit0 ~ 1 によりそれぞれのカウントをイネーブルに出来ます。

bit3のエンコーダ入力の正カウントとは、A相がB相に先行する時にアップカウントし、B相がA相に先行するときにダウンカウントする事です。逆カウントの設定をするとその逆になります。

#### 6-1-4 入力の初期設定レジスタ

表 6-6: 入力の初期設定レジスタ

| bit | 内                  | 容                  |

|-----|--------------------|--------------------|

|     | 0                  | 1                  |

| 0   | +SLD、-SLD は減速入力    | +SLD、-SLD は減速停止入力  |

| 1   | +SLD、-SLD はレベル動作入力 | +SLD、-SLD はエッジ動作入力 |

| 2   | ORG は低感度入力         | ORG は高感度入力         |

| 3   | MARK は低感度入力        | MARK は高感度入力        |

| 4   | CLRA はレベルクリア入力     | CLRA はエッジクリア入力     |

| 5   | 未定義(常に0を設定)        |                    |

| 6   | 未定義(常に0を設定)        |                    |

| 7   | 未定義(常に0を設定)        |                    |

bit0=0 の時に +SLD または -SLD がアクティブになれば、

$R_3$  レジスタ設定の速度に減速( $R_4 > R_3$  の場合)し、パルスの出力を継続します。

bit0=1 の時に +SLD または -SLD がアクティブになれば、 $R_3$  レジスタ設定の速度に減速しパルスの出力を停止します。

#### 6-1-5 入力論理の初期設定レジスタⅠ、Ⅱ

入力論理の初期設定レジスタ I は表 2-1 のデータ 1 でリード、ライトし、入力論理の初期設定レジスタ II はデータ 2 でリード、ライトします。

| bit | 内           | 容          |

|-----|-------------|------------|

|     | 0           | 1          |

| 0   | +EL は負論理入力  | +EL は正論理入力 |

| 1   | -EL は負論理入力  | -EL は正論理入力 |

| 2   | ALM は負論理入力  | ALM は正論理入力 |

| 3   | 未使用(常に0を設定) |            |

| 4   | 未使用(常に0を設定) |            |

| 5   | 未使用(常に0を設定) |            |

| 6   | 未使用(常に0を設定) |            |

| 7   | 未使用(常に0を設定) |            |

表 6-7: 入力論理の初期設定レジスタ [

表 6-8: 入力論理の初期設定レジスタ II

| bit | 内               | 容               |

|-----|-----------------|-----------------|

|     | 0               | 1               |

| 0   | ORG は負論理        | ORG は正論理        |

| 1   | EZ は負論理         | EZ は正論理         |

| 2   |                 | +SLD は正論理入力     |

| 3   | -SLD は負論理入力     | <br>-SLD は正論理入力 |

| 4   | INP は負論理入力      | INP は正論理入力      |

| 5   | <br>MARK は負論理入力 | MARK は正論理入力     |

| 6   | 未使用(常に0を設定)     |                 |

| 7   | 未使用(常に0を設定)     |                 |

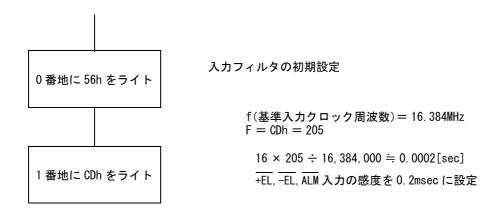

### 6-1-6 入力フィルタの初期設定レジスタ (F)

入力フィルタの設定値は +EL、-EL、ALM、+SLD、-SLD の感度を決めます。 設定値の範囲は 1 ~ 256 です。256 の場合は 0 を設定します。

感度は16×F×基準クロックの1周期です。

# 6-1-7 出力の初期設定レジスタ

表 6-9: 出力の初期設定レジスタ

| bit | 内              | 容         |

|-----|----------------|-----------|

| Dit | 0              | 1         |

| 0   | CLR は 1 ショット出力 | CLR は汎用出力 |

| 1   | 未定義(常に0を設定)    |           |

| 2   | 未定義(常に0を設定)    |           |

| 3   | 未定義(常に0を設定)    |           |

| 4   | 未定義(常に0を設定)    |           |

| 5   | 未定義(常に0を設定)    |           |

| 6   | 未定義(常に0を設定)    |           |

| 7   | 未定義(常に0を設定)    |           |

# 6-1-8 出力論理の初期設定レジスタ

表 6-10: 出力論理の初期設定レジスタ

| bit | 内            | 容            |

|-----|--------------|--------------|

|     | 0            | 1            |

| 0   | POUT は負論理出力  | POUT は正論理出力  |

| 1   | PDIR は負論理出力  | PDIR は正論理出力  |

| 2   | CLR は負論理出力   | CLR は正論理出力   |

| 3   | INT は負論理出力   | INT は正論理出力   |

| 4   | ERROR は負論理出力 | ERROR は正論理出力 |

| 5   | MOVE は負論理出力  | MOVE は正論理出力  |

| 6   | 未定義(常に0を設定)  |              |

| 7   | 未定義(常に0を設定)  |              |

# 7. 制御モードレジスタについて

#### 7-1 各制御モードレジスタの機能

#### 7-1-1 動作制御モード設定レジスタ

表 7-1: 動作制御モード設定レジスタ

| bit | 内             | 容           |

|-----|---------------|-------------|

| Dit | 0             | 1           |

| 0   | 同期スタート制御を行わない | 同期スタート制御を行う |

| 1   | 減速開始点制御コード 1  |             |

| 2   | 減速開始点制御コード 2  |             |

| 3   | 補間制御を行わない     | 補間制御を行う     |

| 4   | 直線加減速モード      | S 字加減速モード   |

| 5   | 放物線           | 正弦          |

| 6   | 未使用(常に0を設定)   |             |

| 7   | 未使用(常に0を設定)   |             |

#### 同期スタート

同期スタート制御を行う場合、 $\underline{\neg \neg \neg}$ ドの  $00h \sim 19h$  のドライブ命令または 40h、41h のタイマ命令後に、同期スタート入力端子の SYNC が HIGH から LOW になればパルス発振またはタイマがスタートします。

#### 減速開始点制御コード

減速開始点制御は、4つのモードがあります。bit1-2で設定します。

| コード 2 | コード 1 | 内 容     |

|-------|-------|---------|

| 0     | 0     | 自動演算    |

| 0     | 1     | オフセット設定 |

| 1     | 0     | マニュアル設定 |

| 1     | 1     | 減速を行わない |

#### 自動演算

このモードは加速レートと減速レートが同じ場合に使用できます。駆動開始時にカウンタDが0クリアされ、駆動中カウント動作を行います。残りパルス数管理用のカウンタCの値が、カウンタDの値以下になれば減速動作を開始します。

起動前にカウンタDのプリセットの必要はありません。

#### オフセット設定

このモードは駆動開始時にカウンタ D が 0 クリアされず、駆動中はカウント動作を行います。 残りパルス数管理用のカウンタ C の値が、カウンタ D の値以下になれば減速動作を開始します。 オフセット値は、駆動前にプリセットします。設定値は、-8,388,608 ~ 8,388,607 で 2 の補数形式で カウンタDにプリセットします。動作は次のようになります。

#### プラス値をプリセットした場合

#### マイナス値をプリセットした場合

#### マニュアル設定

このモードは、減速開始点の管理用カウンタDがカウント動作をせず、レジスタRっとして機能し ます。駆動開始時にも0クリアされません。

残りパルス数管理用のカウンタCの値が、プリセットされたR2レジスタ以下になれば、減速動作を 開始します。

#### 減速開始点動作を行わない

このモードは次のような動作になります。

#### S字加減速

bit4=1のS字加減速モードでは2種類の加減速形状が使用できます。 bit5=0の時は放物線状に、bit5=1の時は正弦関数状になります。

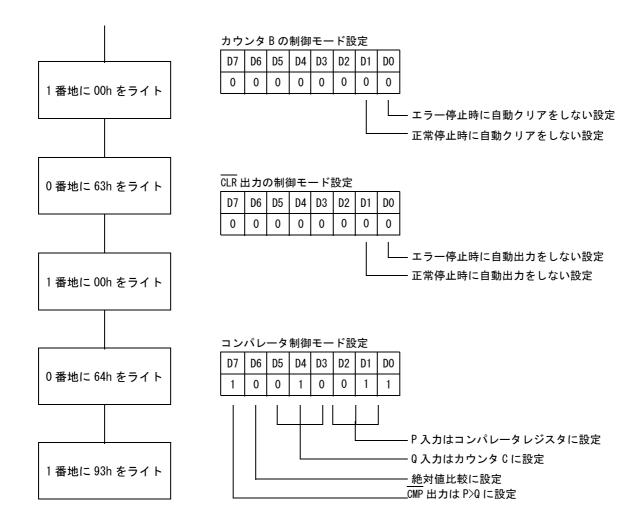

# 7-1-2 カウンタ A、B の制御レジスタ

表 7-2: カウンタ A、Bの制御

| bit | 内              | 容              |

|-----|----------------|----------------|

| Dit | 0              | 1              |

| 0   | エラー停止時に自動クリアせず | エラー停止時に自動クリアする |

| 1   | 正常停止時に自動クリアせず  | 正常停止時に自動クリアする  |

| 2   | 未定義(常に0を設定)    |                |

| 3   | 未定義(常に0を設定)    |                |

| 4   | 未定義(常に0を設定)    |                |

| 5   | 未定義(常に0を設定)    |                |

| 6   | 未定義(常に0を設定)    |                |

| 7   | 未定義(常に0を設定)    |                |

# 7-1-3 CLR 出力制御モードレジスタ

表 7-3:CLR 出力制御モードレジスタ

| bit | 内                   | 容                   |

|-----|---------------------|---------------------|